Full Adder - PowerPoint PPT Presentation

1 / 40

Title:

Full Adder

Description:

Anatomy of a Verilog Module. module. FullAdder (A, B, Cin, Sum, Cout) ... Anatomy of a Verilog Module. input A; Define the input and output ports. module. FullAdder ... – PowerPoint PPT presentation

Number of Views:141

Avg rating:3.0/5.0

Title: Full Adder

1

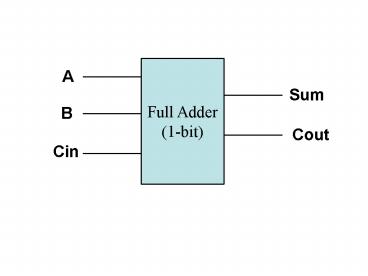

Full Adder (1-bit)

A

Sum

B

Cout

Cin

2

Anatomy of a Verilog Module

3

Anatomy of a Verilog Module

module

Declare a module

4

Anatomy of a Verilog Module

module

Define a module name

FullAdder

5

Anatomy of a Verilog Module

module

FullAdder

(A, B, Cin, Sum, Cout)

Declare the input and output ports

6

Anatomy of a Verilog Module

module

FullAdder

(A, B, Cin, Sum, Cout)

input A

Define the input and output ports

input B

input Cin

output Sum

output Cout

7

Anatomy of a Verilog Module

module

FullAdder

(A, B, Cin, Sum, Cout)

input A

input B

input Cin

output Sum

output Cout

Declare local internal signals

wire AandB, AandCin, xxxx, yyyy, zzzz

8

Anatomy of a Verilog Module

module

FullAdder

(A, B, Cin, Sum, Cout)

input A

input B

input Cin

output Sum

output Cout

wire AandB, AandCin, xxxx, yyyy, zzzz

and(AandB, A, B)

Define circuit using built-in logic

and(AandCin, A, Cin)

9

Anatomy of a Verilog Module

module

FullAdder

(A, B, Cin, Sum, Cout)

input A

input B

input Cin

output Sum

output Cout

wire AandB, AandCin, xxxx, yyyy, zzzz

and(AandB, A, B)

and(AandCin, A, Cin)

endmodule

Define the end of the module

10

1-Bit ALU

Ctrl(0)

Ctrl

Ctrl(1)

A

Full Adder

Carry Control

Cout

A

Cout

B

B

Sum

Cin

Cin

Other logic

A

Result

41 Mux

A

AandB

B

Anot

11

(No Transcript)

12

4-Bit ALU

13

4-Bit ALU

14

4-Bit ALU

15

4-Bit ALU

16

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

17

2-bit vector

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

18

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

19

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

20

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

ALU1Bit ALUBIT2 (A2, B2, Cy1, Ctrl, R2,

Cy2)

21

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

ALU1Bit ALUBIT2 (A2, B2, Cy1, Ctrl, R2,

Cy2)

ALU1Bit ALUBIT3 (A3, B3, Cy2, Ctrl, R3,

Cout)

22

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

ALU1Bit ALUBIT2 (A2, B2, Cy1, Ctrl, R2,

Cy2)

ALU1Bit ALUBIT3 (A3, B3, Cy2, Ctrl, R3,

Cout)

23

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

ALU1Bit ALUBIT2 (A2, B2, Cy1, Ctrl, R2,

Cy2)

ALU1Bit ALUBIT3 (A3, B3, Cy2, Ctrl, R3,

Cout)

24

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

ALU1Bit ALUBIT2 (A2, B2, Cy1, Ctrl, R2,

Cy2)

ALU1Bit ALUBIT3 (A3, B3, Cy2, Ctrl, R3,

Cout)

25

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

ALU1Bit ALUBIT2 (A2, B2, Cy1, Ctrl, R2,

Cy2)

ALU1Bit ALUBIT3 (A3, B3, Cy2, Ctrl, R3,

Cout)

26

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

ALU1Bit ALUBIT2 (A2, B2, Cy1, Ctrl, R2,

Cy2)

ALU1Bit ALUBIT3 (A3, B3, Cy2, Ctrl, R3,

Cout)

27

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

ALU1Bit ALUBIT2 (A2, B2, Cy1, Ctrl, R2,

Cy2)

ALU1Bit ALUBIT3 (A3, B3, Cy2, Ctrl, R3,

Cout)

28

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

ALU1Bit ALUBIT2 (A2, B2, Cy1, Ctrl, R2,

Cy2)

ALU1Bit ALUBIT3 (A3, B3, Cy2, Ctrl, R3,

Cout)

29

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

ALU1Bit ALUBIT2 (A2, B2, Cy1, Ctrl, R2,

Cy2)

ALU1Bit ALUBIT3 (A3, B3, Cy2, Ctrl, R3,

Cout)

30

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

2-bits

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

ALU1Bit ALUBIT2 (A2, B2, Cy1, Ctrl, R2,

Cy2)

ALU1Bit ALUBIT3 (A3, B3, Cy2, Ctrl, R3,

Cout)

31

module ALU1Bit ( A, B, Cin, Ctrl, R,

Cout)

ALU1Bit ALUBIT0 ( A0, B0, Cin, Ctrl, R0,

Cy0)

ALU1Bit ALUBIT1 (A1, B1, Cy0, Ctrl, R1,

Cy1)

ALU1Bit ALUBIT2 (A2, B2, Cy1, Ctrl, R2,

Cy2)

ALU1Bit ALUBIT3 (A3, B3, Cy2, Ctrl, R3,

Cout)

32

Vectors in a DO File

33

Vectors in a DO File

Force the entire vector at the same time

34

Vectors in a DO File

Force the entire vector at the same time

force A 1111 force B 0001

35

Vectors in a DO File

Force the entire vector at the same time

force A 1111 force B 0001

Force the vector one bit at a time

36

Vectors in a DO File

Force the entire vector at the same time

force A 1111 force B 0001

Force the vector one bit at a time

force Ctrl(0) 0, 1 10ns -r 20ns force

Ctrl(1) 0, 1 20ns -r 40ns

37

Vectors in a UCF File

38

Vectors in a UCF File

Each bit of a vector must be mapped individually

39

Vectors in a UCF File

Each bit of a vector must be mapped individually

NET Ctrllt1gt LOC K13 SW7NET Ctrllt0gt

LOC K14 SW6

40

Review of Vector Notation

In a Verilog file Ctrl0 In a DO file

Ctrl(0) In a UCF file Ctrllt0gt