Clock1 PowerPoint PPT Presentations

All Time

Recommended

CLOCK1-DIV2 : This mode is useful for very high performance designs. Clock1 runs at half the speed ... The memory subsystem and the FIFOs are clocked by clock1. ...

| free to download

Reg/Dec: Registers Fetch and Instruction Decode. Exec: Calculate the memory address ... Registers Fetch and Instruction Decode. Exec: compares the two register ...

| free to download

Title: PowerPoint Presentation Author: Songqing Chen Last modified by: IT&E Created Date: 1/15/2003 8:46:02 PM Document presentation format: On-screen Show

| free to download

Low Power Design Techniques Jonathan ... Design Techniques Summary Actel ProASICPlus Design Flow What is Synthesis? The mapping of a behavioral description to a ...

| free to download

Variation of Fundamental Constants V.V. Flambaum School of Physics, UNSW, Sydney, Australia Co-authors: Atomic calculations V.Dzuba, M.Kozlov, E.Angstmann,J.Berengut ...

| free to download

din = 0; wait(); // count up, value = 1. load = false; wait(); // count up, ... signed and unsigned fixed point numbers. User defined constructs. Milenkovic. 9 ...

| free to download

... consecutive transits of the sun is called a solar day ... Fast clock. Perfect clock. dC/dt 1. dC/dt 1. dC/dt = 1. 12/31/09. ICSS741 - Time and Coordination ...

| free to download

Variation of Fundamental Constants V.V. Flambaum School of Physics, UNSW, Sydney, Australia ... Quasar data J.Webb,M.Murphy,M.Drinkwater,W.Walsh,P.Tsanavaris, ...

| free to download

How to fix it? 802.11's Time Sync Function (I) ... How to fix it? Desired properties: simple, efficient, and compatible with current 802.11 TSF. ...

| free to download

Material from The Verilog Hardware Description Language, ... Called inertial delay oddly named, how wide must an input spike be to be seen? a=1 ...

| free to download

Title: C++ Programming: Program Design Including Data Structures, Fifth Edition Last modified by. Created Date: 8/17/2002 1:02:10 AM Document presentation format

| free to view

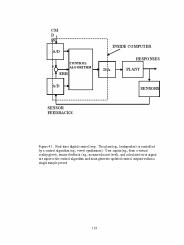

from a virtual reality glove), sensor feedback (eg. ... CATENATE. LF INTO. SOURCE T.S. REGENERATE. ENTIRE. OUTPUT. TIME SERIES. SYNTHETIC. VOICE ...

| free to download

... be implemented in hardware are given to Verilog/VHDL coders ... Verilog or VHDL coders don't understand system design. Problems with standard methodology: ...

| free to download

ELEN 468 Advanced Logic Design Lecture 7 System Tasks, Functions, Syntax and Behavioral Modeling I ELEN 468 Lecture 7 * ELEN 468 Lecture 7 * System Tasks and ...

| free to view

Timed Signals ... A timed process P is strictly causal if it is monotonic, and. For all s: D1 V1, P(s): D2 V2 ... Causal Timed Process Networks ...

| free to view

... 11: Classes and Data Abstraction. Objectives. In this chapter ... Learn about the abstract data type (ADT) ... Abstraction can also be applied to ...

| free to view

Title: Device Support Author: Kazuro Furukawa Last modified by: f k Created Date: 7/6/2006 3:35:54 PM Document presentation format: A4 Company

| free to download

provide a method of referencing the memory location of variables. analogy in real world: ... Log on to Yahoo! Instant Messenger (I will send you an INVITE to join a ...

| free to view

Timing and data exchange D.Autiero/IN2P3 Lyon, 15/1/07 GPS Timing: Calibrations Results from the CNGS run Perspectives EW and Database STATUS WORD WHAT Basic ...

| free to view

DatagramPacket et DatagramServer repr sente les points de connexion UDP ... Certificate : atteste qu'une cl publique est celle du propri taire. ...

| free to download

[aspect, audiospectogram, auspices, auspicious, cacospectamania, chronospecies, ... prospective, prospectus, respect, respective, respite, retrospect, special, ...

| free to view

Material from The Verilog Hardware Description Language, ... Here's how gate-level Verilog is executed ... Verilog Gate Level Timing Model ...

| free to view