Implementing High Level Integer Arithmetic Operations 1 PowerPoint PPT Presentation

1 / 9

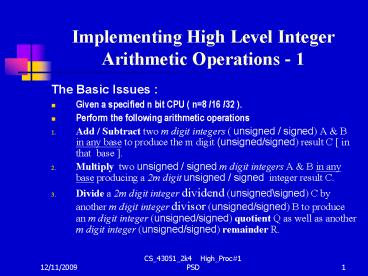

Title: Implementing High Level Integer Arithmetic Operations 1

1

Implementing High Level Integer Arithmetic

Operations - 1

- The Basic Issues

- Given a specified n bit CPU ( n8 /16 /32 ).

- Perform the following arithmetic operations

- Add / Subtract two m digit integers ( unsigned /

signed) A B in any base to produce the m digit

(unsigned/signed) result C in that base . - Multiply two unsigned / signed m digit integers

A B in any base producing a 2m digit unsigned /

signed integer result C. - Divide a 2m digit integer dividend

(unsigned\signed) C by another m digit integer

divisor (unsigned/signed) B to produce an m digit

integer (unsigned/signed) quotient Q as well as

another m digit integer (unsigned/signed)

remainder R.

2

Implementing High Level Integer Arithmetic

Operations - 2

- The Facts the associated assumptions

- The Fact An m digit integer (signed/unsigned),

in any base when converted to binary yields a k

bit binary integer (signed/unsigned) where k gt

n and k need not be an integer multiple of n. - The Assumptions

- All Operands A , B OR C as well as the Results

( C , Q R) are expressed as integer multiples

of n. ( The CPU Size) and all of them are stored

in memory. Each is expressed in HEX. - The CPU size ( n ) is a power of 2 I.e. n 2 j

where j has one of the following integer values

2 4 bit CPU , 3 8 bit CPU , 4 16 bit CPU

or 5 32 bit CPU. We assume here j 5 I.e. n

32. - Memory is having 32 bit address, speed compatible

with CPU, alterable and byte organized. - Everything in memory is stored in n bit word

boundary in Little Endian convention, in

consecutive locations starting from a000 0000H

3

The Memory Storage Pattern

- Assume A 3e 4b 6c bf 67 79 88 ae 7b ee fd ae ff

b8 a9 bf Hex 16 bytes - B f4 56 ab 56 78 99 8b 6e de fa

88 98 ac Hex 13 bytes - ff ff ff f4 56 ab 56 78 99

8b 6e de fa 88 98 ac Hex 16 bytes - After sign Extension

- C A op B 1d 2e .. .. .. .. .. .. bf 67 bf

de ae ff Hex 16 byte Result - Variable Memory Offset

Content - --------------------------------------------------

------------ - A a000 0000H

a9 - --------------------------------------------------

------------ - A1 a000 0001 H

b8 - .. A15 a000 000f H

3e - --------------------------------------------------

------------ - .. B a000 0010 H

ac - B15 a000 001f H

ff - --------------------------------------------------

----------- - C a000 0020 H

ff - .. C15 a000 002f H

1d

4

Our Assumptions Contd.

- A 32 bit CPU with 32 bit Data Bus 32 bit

Address Bus. - 8 Number of 32 bit GPRs r0 .. r7.

- All operands must be brought inside some of the

GPRs of the CPU before any processing. - The 32 bit ALU is involved in all types of

processing. - All results (intermediate as well as final) are

first generated and stored inside some GPR of the

CPU.

5

The Addition / Subtraction Operation

- Task at hand

- Given Operand A 128 bit long stored from

location a000 0000H. - Operand B 128 bit long stored from location

a000 0010 H. - To Compute C A PLUS B OR A MINUS B with C to be

stored from location a000 0020 H. - All values are stored using little Endian

conventions.

6

The Addition Operation Steps

- Set up Word Counter . r5 ? 4

- Clear CARRY Flag.

- Set up address pointer for Operand A r0 ?

Addr. of A . - Set up address pointer for Operand B r1 ?

Addr. of B . - Set up address pointer for Operand C r2 ?

Addr. of C . - Load a GPR with the Current Word of Opnd. A r6

? M(r0) . - Load a GPR with the Current Word of Opnd. B r7

? M(r1). - Add with Carry r6 ? (r6) PLUS (Sr7). PLUS

(Cy). Ignore Overflow. - Store Result in Current Word of Operand C

M(r2) ? r6. - Increment Address Pointers r0 (A) , r1(B),

r2(C) . - Decrement Word Counter r5.

- If Word Counter 0 GOTO EXIT ELSE GOTO Step 6.

- EXIT Check Overflow Generate App. Message

GOTO Monitor.

7

The Subtraction Operation Steps

- Set up Word Counter . r5 ? 4

- Clear CARRY/ BORROW Flag.

- Set up address pointer for Operand A r0 ?

Addr. of A . - Set up address pointer for Operand B r1 ?

Addr. of B . - Set up address pointer for Operand C r2 ?

Addr. of C . - Load a GPR with the Current Word of Opnd. A r6

? M(r0) . - Load a GPR with the Current Word of Opnd. B r7

? M(r2). - Invert CARRY / BORROW Flag,

- Subtract with Borrow r6 ? (r6) MINUS (Sr7)

MINUS Cy. Ignore Overflow. - Store Result in Current Word of Operand C

M(r2) ? r6. - Increment Address Pointers r0 (A) , r1(B),

r2(C) . - Decrement Word Counter r5.

- If Word Counter 0 GOTO EXIT ELSE GOTO Step 5.

- EXIT Check Overflow Generate App. Message

GOTO Monitor.

8

Multiplication

- Following two ( 2 ) types of operations

- 1) Unsigned Multiplication

- C A X B where A B each happens to be

unsigned n digit operands C is the unsigned 2n

digit result. - 2) Signed Multiplication

- C A X B where A B each happens to be signed

- ( rs complement) n digit operands C is the

signed (rs complement) 2n digit result. In each

case the MS Digit stores the sign.

9

Division

- Following two ( 2 ) types of operations

- 1) Unsigned Division

- C / A yielding Q R such that C Q X A R

- where C is the unsigned 2n digit Dividend.

- A is the unsigned n digit divisor.

- Q is the unsigned n digit quotient.

- R is the unsigned n digit remainder.

- 2) Signed Division

- C / A yielding Q R such that C Q X A R

- where C is the signed 2n digit Dividend.

- A is the signed(rs complement) n digit

divisor. - Q is the signed (rs complement) n digit

quotient. - R is the signed (rs complement) n digit

remainder ( same sign as C).