Diseo de controladores digitales PowerPoint PPT Presentation

1 / 44

Title: Diseo de controladores digitales

1

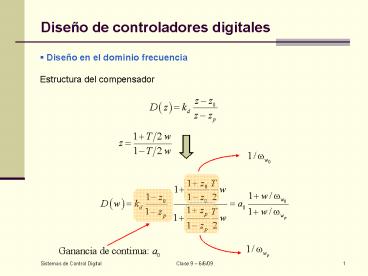

Diseño de controladores digitales

- Diseño en el dominio frecuencia

- Estructura del compensador

2

Diseño de controladores digitales

- Diseño en el dominio frecuencia

- Procedimiento de diseño

Transformación

Diseño en w

3

Diseño de controladores digitales

- Diseño en el dominio frecuencia

- Obtención del controlador discreto

4

Diseño de controladores digitales

- Diseño en el dominio frecuencia

- Compensador de retraso de fase (LAG)

Efecto deseadoIncremento de ganancia en baja

frecuencia (o atenuación en alta) Efecto

indeseadoRetraso de fase

Ubicar el compensador donde el retraso de fase no

perjudique el margen de fase

5

Diseño de controladores digitales

- Diseño en el dominio frecuencia

- Compensador de retraso de fase (LAG) - Efecto

6

Diseño de controladores digitales

- Diseño en el dominio frecuencia

- Guía para el diseño del compensador de retraso de

fase (LAG) - Seleccionar la ganancia (a0) del compensador para

satisfacer requerimiento de error estacionario o

MF. - Determinar la frecuencia de cruce deseada

(inferior a la de lazo abierto). - Ubicar el cero del compensador 10 veces por

debajo de la frecuencia de cruce. - Calcular el polo del compensador para tener

ganancia unitaria a la frecuencia de cruce.

7

Diseño de controladores digitales

- Diseño en el dominio frecuencia

- Compensador de adelanto de fase (LEAD)

Efecto deseadoAporte de fase. Efecto

indeseadoIncremento de la ganancia de alta

frecuencia.

8

Diseño de controladores digitales

- Diseño en el dominio frecuencia

- Compensador de adelanto de fase (LEAD)

El aporte de fase máximo está dado por la

distancia relativa entre el cero y el polo del

compensador

9

Diseño de controladores digitales

- Diseño en el dominio frecuencia

- Compensador de adelanto de fase (LEAD) - Efecto

10

Diseño de controladores digitales

- Diseño en el dominio frecuencia

- Guía para el diseño del compensador de adelanto

de fase (LEAD) - Seleccionar la ganancia (a0) del compensador para

satisfacer requerim. de error estacionario o

frecuencia de cruce (ancho de banda). - Evaluar el margen de fase del sistema no

compensado MF. - Determinar el aporte de fase necesario

- Determinar la separación polo-cero.

- Determinar la nueva frecuencia de cruce donde

- Evaluar el MF del sistema compensado. De ser

necesario, iterar o agregar etapas

11

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LAG

- Especificaciones

- Mantener el error estacionario

- No aumentar el ancho de banda

- Mejorar el transitorio (MF55º)

12

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LAG (cont.) Evaluamos la respuesta

en frecuencia de

13

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LAG (cont.) Evaluamos la respuesta

en frecuencia de

60º

14

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LAG (cont.) Evaluamos la respuesta

en frecuencia de

15

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LAG (cont.) Evaluamos los márgenes

resultantes

16

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LAG (cont.) Evaluamos la respuesta

en frecuencia de lazo cerrado

17

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LAG (cont.) Evaluamos la respuesta

temporal ante entrada escalón

18

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LEAD Para la misma planta que en

el diseño LAG

- Especificaciones

- Mantener el error estacionario

- No disminuir el ancho de banda

- Mejorar el transitorio (MF55º)

19

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LEAD (cont.) Evaluamos la

respuesta en frecuencia de

- Mantenemos ganancia de continua (a01).

- MF del sistema sin compensar MF31.5º.

- Adelanto necesario

- Separación polo-cero

MF31.5º

20

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LEAD (cont.) Evaluamos la

respuesta en frecuencia de

- Ubicamos el aporte máximo del comp.para

aprovecharlo mejor

-4.77dB

21

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LEAD (cont.) Evaluamos la

respuesta en frecuencia de

- Evaluamos el MF del sistema compensadoMF44º

Insuficiente

MF44º

22

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LEAD (cont.) Evaluamos la

respuesta en frecuencia de

- Iteramos subiendo el polo

- MF45.4º Insuficiente

MF45.4º

23

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LEAD (cont.) Evaluamos la

respuesta en frecuencia de

- Iteramos subiendo el polo

Diseño OK

MF54.8º

24

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LEAD (cont.) Evaluamos la

respuesta en frecuencia de lazo cerrado

25

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo diseño LEAD (cont.) Evaluamos la

respuesta temporal ante entrada escalón

26

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplos de diseño Comparación

(cont.) Respuestas en frecuencia de lazo abierto

27

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplos de diseño Comparación

(cont.) Respuestas en frecuencia de lazo cerrado

28

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplos de diseño Comparación Respuestas

temporales ante entrada escalón - Salida

29

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplos de diseño Comparación

(cont.) Respuestas temporales ante entrada

escalón Esfuerzo de control

30

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo de diseño (Idem al utilizado en LR)

31

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo de diseño (cont.) Respuesta en frecuencia

de lazo abierto

32

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo de diseño (cont.) Diseño LEAD Respuesta

en frecuencia de lazo abierto

- Mantenemos ganancia de continua (a01).

- MF del sistema sin compensar MF10º.

- Adelanto necesario

- Separación polo-cero

MF10º

33

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo de diseño (cont.) Respuesta en frecuencia

de lazo abierto

- Ubicamos el aporte máximo del comp.para

aprovecharlo mejor

-7.83dB

34

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo de diseño (cont.) Respuesta en frecuencia

de lazo abierto compensado

- Evaluamos el MF del sistema compensadoMF43.4º

Insuficiente

MF43.4º

35

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo de diseño (cont.) Respuesta en frecuencia

de lazo abierto compensado

- Iteramos bajando el cero

MF37.1º Insuficiente

MF37.1º

36

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo de diseño (cont.) Respuesta en frecuencia

de lazo abierto compensado

- Iteramos subiendo el polo

MF54.6º Diseño OK

MF54.6º

37

Diseño de controladores digitales

- Diseño en el dominio frecuencia

Ejemplo de diseño (cont.) Respuesta al escalón

del sistema compensado

Cumple especificaciones

38

Diseño de controladores digitales

- Diseño en el dominio frecuencia - Controladores

PD, PI y PID

Ejemplo de diseño (Mismo sistema utilizado en el

LAG)

- Especificaciones

- Error estacionario a la rampa de 0.5

- Mejorar el transitorio (MF55º)

39

Diseño de controladores digitales

- Diseño en el dominio frecuencia - Controladores

PD, PI y PID

Ejemplo de diseño (cont.) Respuesta en frecuencia

de lazo abierto

Controlador PI

40

Diseño de controladores digitales

- Diseño en el dominio frecuencia - Controladores

PD, PI y PID

Ejemplo de diseño (cont.) Respuesta en frecuencia

de lazo abierto

Controlador PI

41

Diseño de controladores digitales

- Diseño en el dominio frecuencia - Controladores

PD, PI y PID

Ejemplo de diseño (cont.) Respuesta temporal

Controlador PI

42

Diseño de controladores digitales

- Diseño en el dominio frecuencia - Controladores

PD, PI y PID

Ejemplo de diseño (cont.) Respuesta en frecuencia

de lazo abierto

Controlador PID

43

Diseño de controladores digitales

- Diseño en el dominio frecuencia - Controladores

PD, PI y PID

Ejemplo de diseño (cont.) Respuesta en frecuencia

de lazo abierto

Controlador PID

44

Diseño de controladores digitales

- Diseño en el dominio frecuencia - Controladores

PD, PI y PID

Ejemplo de diseño (cont.) Respuesta temporal

Controlador PID