OUTLINE PowerPoint PPT Presentation

1 / 20

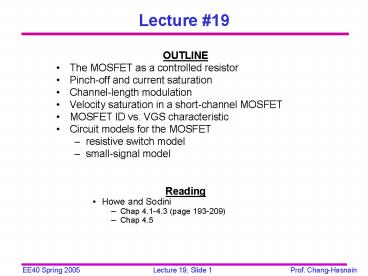

Title: OUTLINE

1

Lecture 19

- OUTLINE

- The MOSFET as a controlled resistor

- Pinch-off and current saturation

- Channel-length modulation

- Velocity saturation in a short-channel MOSFET

- MOSFET ID vs. VGS characteristic

- Circuit models for the MOSFET

- resistive switch model

- small-signal model

- Reading

- Howe and Sodini

- Chap 4.1-4.3 (page 193-209)

- Chap 4.5

2

MOSFET Terminals

- The voltage applied to the GATE terminal

determines whether current can flow between the

SOURCE DRAIN terminals. - For an n-channel MOSFET, the SOURCE is biased at

a lower potential (often 0 V) than the DRAIN - (Electrons flow from SOURCE to DRAIN when VG gt

VT) - For a p-channel MOSFET, the SOURCE is biased at a

higher potential (often the supply voltage VDD)

than the DRAIN - (Holes flow from SOURCE to DRAIN when VG lt VT )

- The BODY terminal is usually connected to a fixed

potential. - For an n-channel MOSFET, the BODY is connected to

0 V - For a p-channel MOSFET, the BODY is connected to

VDD

3

MOSFET Circuit Symbols

G

G

NMOS

n

n

S

S

G

G

PMOS

p

p

S

S

4

The MOSFET as a Controlled Resistor

- The MOSFET behaves as a resistor when VDS is low

- Drain current ID increases linearly with VDS

- Resistance RDS between SOURCE DRAIN depends on

VGS - RDS is lowered as VGS increases above VT

- NMOSFET Example

oxide thickness ? tox

ID

VGS 2 V

VGS 1 V gt VT

VDS

Inversion charge density Qi(x)

-CoxVGS-VT-V(x) where Cox ? eox / tox

IDS 0 if VGS lt VT

5

Sheet Resistance Revisited

Consider a sample of n-type semiconductor

where Qn is the charge per unit area

6

MOSFET as a Controlled Resistor (contd)

average value of V(x)

- We can make RDS low by

- applying a large gate drive (VGS ? VT)

- making W large and/or L small

7

Charge in an N-Channel MOSFET

VGS lt VT

depletion region

(no inversion layer at surface)

VGS gt VT

VDS ? 0

VDS gt 0 (small)

Average electron velocity v is proportional to

lateral electric field E

8

What Happens at Larger VDS?

VGS gt VT

VDS VGSVT

Inversion-layer is pinched-off at the drain end

VDS gt VGSVT

- As VDS increases above VGSVT ? VDSAT,

- the length of the pinch-off region DL

increases - extra voltage (VDS VDsat) is dropped across

the distance DL - the voltage dropped across the inversion-layer

resistor remains VDsat - the drain current ID saturates

Note Electrons are swept into the drain by the

E-field when they enter the pinch-off region.

9

Summary of ID vs. VDS

- As VDS increases, the inversion-layer charge

density at the drain end of the channel is

reduced therefore, ID does not increase linearly

with VDS. - When VDS reaches VGS ? VT, the channel is

pinched off at the drain end, and ID saturates

(i.e. it does not increase with further increases

in VDS).

pinch-off region

10

ID vs. VDS Characteristics

- The MOSFET ID-VDS curve consists of two regions

- 1) Resistive or Triode Region 0 lt VDS lt VGS ?

VT - 2) Saturation Region

- VDS gt VGS ? VT

process transconductance parameter

CUTOFF region VG lt VT

11

Channel-Length Modulation

- If L is small, the effect of DL to reduce the

inversion-layer resistor length is significant - ID increases noticeably with DL (i.e. with VDS)

ID

ID ID?(1 lVDS)

l is the slope

ID? is the intercept

VDS

12

Current Saturation in Modern MOSFETs

- In digital ICs, we typically use transistors with

the shortest possible gate-length for high-speed

operation. - In a very short-channel MOSFET, ID saturates

because the carrier velocity is limited to 107

cm/sec

v is not proportional to E, due to velocity

saturation

13

Consequences of Velocity Saturation

1. ID is lower than that predicted by the

mobility model 2. ID increases linearly with VGS

? VT rather than quadratically in the saturation

region

14

P-Channel MOSFET ID vs. VDS

- As compared to an n-channel MOSFET, the signs of

all the voltages and the currents are reversed - Note that the effects

- of velocity saturation

- are less pronounced

- than for an NMOSFET.

- Why is this the case?

Short-channel PMOSFET I-V

15

MOSFET ID vs. VGS Characteristic

- Typically, VDS is fixed when ID is plotted as a

function of VGS

Long-channel MOSFET VDS 2.5 V gt VDSAT

Short-channel MOSFET VDS 2.5 V gt VDSAT

16

MOSFET VT Measurement

- VT can be determined by plotting ID vs. VGS,

using a low value of VDS

ID (A)

VGS (V)

0

VT

17

Subthreshold Conduction (Leakage Current)

- The transition from the ON state to the OFF state

is gradual. This can be seen more clearly when

ID is plotted on a logarithmic scale - In the subthreshold

- (VGS lt VT) region,

- This is essentially the channel-

- source pn junction current.

- (Some electrons diffuse from the

- source into the channel, if this

- pn junction is forward biased.)

VDS gt 0

18

Qualitative Explanation for Subthreshold Leakage

- The channel Vc (at the Si surface) is

capacitively coupled to the gate voltage VG

Using the capacitive voltage divider formula

(Lecture 12, Slide 7)

CIRCUIT MODEL

DEVICE

VG

VG

VD

n poly-Si

Cox

Vc

n

n

Cdep

The forward bias on the channel-source pn

junction increases with VG scaled by the factor

Cox / (CoxCdep)

Wdep

depletion region

p-type Si

19

Slope Factor (or Subthreshold Swing) S

- S is defined to be the inverse slope of the log

(ID) vs. VGS characteristic in the subthreshold

region

VDS gt 0

Units Volts per decade Note that S 60

mV/dec at room temperature

1/S is the slope

20

VT Design Trade-Off(Important consideration for

digital-circuit applications)

- Low VT is desirable for high ON current

- IDSAT ? (VDD - VT)? 1 lt ? lt 2

- where VDD is the power-supply voltage

- but high VT is needed for low OFF current

log IDS

Low VT

High VT

IOFF,low VT

IOFF,high VT

VGS

0