Discussion - PowerPoint PPT Presentation

1 / 85

Title:

Discussion

Description:

11 Yea, by the power of his voice doth the whole earth shake; ... Anatomy of an Instruction. 15. 14. 13. 12. 11. 10. 9. 8. 7. 6. 5. 4. 3. 2. 1. 0. 0. 0. 1. 0 ... – PowerPoint PPT presentation

Number of Views:60

Avg rating:3.0/5.0

Title: Discussion

1

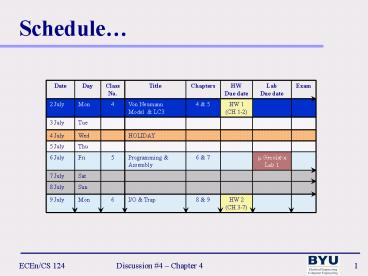

Schedule

2

Chapter 4 The Von Neumann Model

3

Instructions

- Helaman 126-13

- 6 Behold, they do not desire that the Lord

their God, who hath created them, should rule and

reign over them notwithstanding his great

goodness and his mercy towards them, they do set

at naught his counsels, and they will not that he

should be their guide. - 7 O how great is the nothingness of the

children of men yea, even they are less than the

dust of the earth. - 8 For behold, the dust of the earth moveth

hither and thither, to the dividing asunder, at

the command of our great and everlasting God. - 9 Yea, behold at his voice do the hills and the

mountains tremble and quake. - 10 And by the power of his voice they are

broken up, and become smooth, yea, even like unto

a valley. - 11 Yea, by the power of his voice doth the

whole earth shake - 12 Yea, by the power of his voice, do the

foundations rock, even to the very center. - 13 Yea, and if he say unto the earthMoveit is

moved.

4

Digital Logic Hierarchy

Now Begins Software

5

The Von Neumann Computer

Von Neumannproposed this model in 1946

Datapath

Control

The Von Neumann modelProgram instructions and

Data are both stored as sequencesof bits in

computer memory

6

Memory Interface

- Memory Address Register(MAR) stores the

memoryaddress that is to be read orwritten - Memory Data Register (MDR) stores

- The data that is read from memory

- The data this is to be written to memory

- Memory Write Enable (WE) is a control signal that

is asserted to write memory

7

Memory Terminology

- Address Space amount of data that can be stored

(also called the memory size) - Addressability number of bits stored in each

memory location - 1 byte 8 bits

- 1 Kilobyte (Kbyte) 210 bytes 1024 bytes

- 1 Megabyte (Mbyte) 220 bytes

- 1 Gigabyte (Gbyte) 230 bytes

8

The Processing Unit

- ALU Arithmetic and Logic Unit

- ADD, SUB, MULT, etc.

- AND, OR, NOT, etc.

- word length the number of bits processed by the

ALU. - Includes a small amount of memory very close to

the ALU (like a register file)

INPUT

OUTPUT

Processing Unit

ALU

TEMP

Control Unit

PC

IR

9

Input and Output

- Used to get information in and out of the

computer. - External devices attached to a computer are

called peripherals.

INPUT keyboard mouse scanner card

reader disk

OUTPUT monitor printer LED disk

Processing Unit

ALU

TEMP

Control Unit

PC

IR

10

Control

- The control unit directs the execution of the

program - It keeps track of

- Where we are in the process of executing the

program - The program counter or PC points to the next

instruction to be executed - Where we are in the process of executing the

current - The instruction register or IR contains the

currently executing instruction

INPUT

Processing Unit

ALU

TEMP

Control Unit

PC

IR

11

The LC-3 An Example Von Neumann Machine

PC

IR

12

Anatomy of an Instruction

ADD R6,R2,R6

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

1

1

1

0

0

1

0

0

0

0

1

1

0

13

The Instruction Cycle

- FETCH

- Obtain the next instruction from memory

- DECODE

- Examine the instruction, and determine how to

execute it - EVALUATE ADDRESS

- Compute the address of the memory location (put

in MAR) - FETCH OPERANDS

- Obtain the source operands

- EXECUTE

- Carry out the execution of the instruction

- STORE RESULT

- Store the result in the designated destination

Not all instructions require all six phases

14

The Fetch Phase

- Computer programs consist of instructions

- Each instruction 1 Binary Word 16 bits

- Instructions are stored in memory

- Program sequence of instructions

- stored in memory as 1s and 0s

- called machine code (Chapter 1)

15

Fetching an Instruction

ADD R6,R2,R6

- Copy PC contents to MAR, and PC is incremented

PC

- Wait for memory access

- Result will be placed into MDR by memory unit

- Copy MDR contents to IR

IR

?

16

Decode

ADD R6,R2,R6

- Pick apart the instruction stored in the IR

- control unit in control logic does all this

- Determine

- operation

- operand sources

- operand destination

17

Fetch Operands

ADD R6,R2,R6

PC

IR

18

Execute

ADD R6,R2,R6

- The ALU doesits operation

- control unittells it whichoperation to do

PC

IR

19

Store Result

ADD R6,R2,R6

PC

IR

20

An LDR Instruction

LDR,R2,R3,6

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

1

1

0

0

1

0

0

1

1

0

0

0

1

1

0

EffectiveAddress (contents of R3) 6 R2

MEMEffectiveAddress

This requires the computation of an effective

memory address. It is base offset. The

contents of R3 are the base address and 6 is the

offset.

21

Fetch Operands

LDR,R2,R3,6

PC

IR

22

Evaluate AddressRead Memory

LDR,R2,R3,6

PC

IR

23

Store Result

LDR,R2,R3,6

PC

IR

24

A JMP Instruction

JMP R3

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

1

1

0

0

0

0

0

0

1

1

0

0

0

0

0

0

EffectiveAddress (contents of R3) PC

EffectiveAddress

This is how a GOTO statement would be executed.

25

Fetch Operands

JMP R3

PC

IR

26

Execute

JMP R3

- The ALU doesits operation

- control unittells it whichoperation to do

PC

IR

27

Store Result

JMP R3

PC

IR

28

Von Neumann In Review

- Programs are stored in memory as instructions

- our LC-3 machine has 16-bit instructions

- Data is also stored in memory

- A program is executed by

- fetching next instruction from memory

- decoding it

- evaluating its address

- fetching its operands

- doing the requested operation and

- storing the result

29

The Von Neumann Bottleneck

- You may hear of the term Von Neumann Bottleneck

- All instructions have to be fetched from memory

- the path to memory is a bottleneck

- In spite of this, the Von Neumann model is the

computing model that is used

30

Chapter 5The LC-3

31

Instruction Set Architecture (ISA)

- The computer ISA defines all of the

programmer-visible components and operations of

the computer - memory organization

- address space -- how may locations can be

addressed? - addressibility -- how many bits per location?

- register set

- how many? what size? how are they used?

- instruction set

- opcodes

- data types

- addressing modes

- ISA provides all information needed for someone

that wants to write a program in machine language

(or translate from a high-level language to

machine language).

32

LC-3 Overview Instruction Set

- The LC-3 is a 16-bit Machine

- ALU is 16-bits wide

- all instructions fit into a 16-bit word

- 15 Defined Opcodes

- Operate instructions ADD, AND, NOT

- Data movement instructions LD, LDI, LDR, LEA,

ST, STR, STI - Control instructions BR, JSR/JSRR, JMP, RTI,

TRAP - Condition codes are set/cleared based on a

register result - Data Types

- 16-bit 2s complement integer

- Addressing Modes

- non-memory addresses immediate, register

- memory addresses PC-relative, indirect,

baseoffset

33

LC-3 Overview Memory and Registers

- Memory

- address space 216 locations (65,536)

- addressability 16 bits (2 bytes)

- total memory size is 131,072 bytes

- Registers

- temporary storage, accessed in a single machine

cycle - eight general-purpose registers R0 - R7

- each 16 bits wide

- how many bits to uniquely identify a register?

- other registers

- not directly addressable, but used by (and

affected by) instructions - PC (program counter), IR (instruction register),

condition codes

34

LC-3 Overview Data Types

- LC-3 has only one data type

- a 16-bit 2s complement Integer

- Other computers have others

- 32-bit floating point (float)

- 64-bit floating point (double)

- long twice the number of bits as Integer

- short half the number of bits as Integer

- Byte 8-bit Integer, or Character (char)

35

All Instructions

36

Operate Instructions

- Only three operations ADD, AND, NOT

- Source and destination operands are registers

- These instructions do not reference memory.

- ADD and AND can use immediate mode,where one

operand is hard-wired into the instruction. - Will show dataflow diagram with each instruction.

- illustrates when and where data moves to

accomplish the desired operation

37

NOT (Register)

Operate Instructions

Note Src and Dstcould be the same register.

38

NOT DR NOT SR1

Operate Instructions

PC

Not B

IR

39

ADD/AND (Register)

Operate Instructions

this zero means register mode

40

ADD DR SR1 SR2

Operate Instructions

PC

IR(5)0

Add

IR

41

AND DR SR1 AND SR2

Operate Instructions

PC

IR(5)0

And

IR

42

ADD/AND (Immediate)

Operate Instructions

this one means immediate mode

Note Immediate field issign-extended.

43

ADD DR SR1 immed5

Operate Instructions

PC

IR(5)1

Add

IR

44

AND DR SR1 AND immed5

Operate Instructions

PC

IR(5)1

And

IR

45

Using Operate Instructions

Operate Instructions

- With only ADD, AND, NOT

- How do we subtract?

- How do we OR?

- How do we copy from one register to another?

- How do we initialize a register to zero?

46

Data Movement Instructions

Data Movement Instructions

- Load -- read data from memory to register

- LD PC-relative mode

- LDR baseoffset mode

- LDI indirect mode

- Store -- write data from register to memory

- ST PC-relative mode

- STR baseoffset mode

- STI indirect mode

- Load effective address -- compute address, save

in register - LEA immediate mode

- does not access memory

47

PC-Relative Addressing Mode

Data Movement Instructions

- Want to specify address directly in the

instruction - But an address is 16 bits, and so is an

instruction! - After subtracting 4 bits for opcodeand 3 bits

for register, we have 9 bits available for

address. - Solution

- Use the 9 bits as a signed offset from the

current PC. - 9 bits

- Can form any address X, such that

- Remember that PC is incremented as part of the

FETCH phase - This is done before the EVALUATE ADDRESS stage.

48

LD (PC-Relative)

Data Movement Instructions

49

LD DR MemPC Offset9

Data Movement Instructions

PC

IR

50

ST (PC-Relative)

Data Movement Instructions

51

ST MemPC Offset9 SR

Data Movement Instructions

PC

SR

IR

52

Indirect Addressing Mode

Data Movement Instructions

- With PC-relative mode, can only address data

within 256 words of the instruction. - What about the rest of memory?

- Solution 1

- Read address from memory location,then

load/store to that address. - First address is generated from PC and IR(just

like PC-relative addressing), thencontent of

that address is used as target for load/store.

53

LDI (Indirect)

Data Movement Instructions

54

LDI DR MemMemPC Offset9

Data Movement Instructions

PC

IR

55

STI (Indirect)

Data Movement Instructions

56

STI MemMemPC Offset9 SR

Data Movement Instructions

PC

SR

IR

57

Base Offset Addressing Mode

Data Movement Instructions

- With PC-relative mode, can only address data

within 256 words of the instruction. - What about the rest of memory?

- Solution 2

- Use a register to generate a full 16-bit address.

- 4 bits for opcode, 3 for src/dest register,3

bits for base register -- remaining 6 bits are

usedas a signed offset. - Offset is sign-extended before adding to base

register.

58

LDR (BaseOffset)

Data Movement Instructions

59

LDR DR MemBaseR Offset6

Data Movement Instructions

PC

BaseR

IR

60

STR (BaseOffset)

Data Movement Instructions

61

STR MemBaseR Offset6 SR

Data Movement Instructions

PC

SR

BaseR

IR

62

Load Effective Address (LEA)

Data Movement Instructions

- Computes address like PC-relative (PC plus signed

offset) and stores the result into a register. - Note The address is stored in the register, not

the contents of the memory location.

63

LEA (Immediate)

Data Movement Instructions

64

LEA DR PC Offset9

Data Movement Instructions

PC

IR

65

Example

Data Movement Instructions

66

Control Instructions

Control Instructions

- Used to alter the sequence of instructions (by

changing the PC) - Conditional Branch

- branch is taken if a specified condition is true

- signed offset is added to PC to yield new PC

- else, the branch is not taken

- PC is not changed, points to the next sequential

instruction - Unconditional Branch (or Jump)

- always changes the PC

- TRAP

- changes PC to the address of an OS service

routine - routine will return control to the next

instruction (after TRAP)

67

Condition Codes

Control Instructions

- LC-3 has three condition code registers N --

negative Z -- zero P -- positive (greater than

zero) - Set by any instruction that writes a value to a

register(ADD, AND, NOT, LD, LDR, LDI, LEA) - Exactly one will be set at all times

- Based on the last instruction that altered a

register

68

All Instructions

ADD

LD

DR

SR1

SR2

DR

0001

00

0

0010

PCoffset9

ADD

LDI

DR

imm5

1010

PCoffset9

0001

DR

SR1

1

AND

DR

SR1

SR2

LDR

DR

0101

00

BaseR

0

0110

offset6

AND

LEA

DR

imm5

0101

DR

SR1

1

1110

PCoffset9

NOT

DR

SR

SR

1001

111111

ST

0011

PCoffset9

BR

STI

z

p

0000

n

PCoffset9

PCoffset9

SR

1011

JMP

STR

SR

BaseR

1100

0

000000

00

0111

offset6

BaseR

JSR

TRAP

PCoffset11

0100

1

1111

trapvect8

0000

RTI

JSRR

BaseR

1000

000000000000

0100

0

000000

00

RET

reserved

111

1101

1100

0

000000

00

69

Branch Instruction

Control Instructions

- Branch specifies one or more condition codes.

- If the set bit is specified, the branch is taken.

- PC-relative addressingtarget address is made by

adding signed offset (IR80)to current PC. - Note PC has already been incremented by FETCH

stage. - Note Target must be within 256 words of BR

instruction. - If the branch is not taken,the next sequential

instruction is executed.

70

BR (PC-Relative)

Control Instructions

What happens if bits 119 are all zero? All

one?

71

Branch if (COND) PC PC PCoffset9

Control Instructions

LD ifCOND

PC

COND

IR

72

Using Branch Instructions

Control Instructions

- Compute sum of 12 integers.Numbers start at

location x3100. Program starts at location x3000.

R1 ? x3100R3 ? 0R2 ? 12

R20?

R4 ? MR1R3 ? R3R4R1 ? R11 R2 ? R2-1

NO

YES

73

Sample Program

Control Instructions

74

JMP (Register)

Control Instructions

- Jump is an unconditional branch -- always taken.

- Target address is the contents of a register.

- Allows any target address.

75

Jump PC BaseR

Control Instructions

PC

BaseR

IR

76

TRAP

Control Instructions

- Calls a service routine, identified by 8-bit

trap vector. - When routine is done, PC is set to the

instruction following TRAP.

77

Another Example

An Example

- Count the occurrences of a character in a file

- Program begins at location x3000

- Read character from keyboard

- Load each character from a file

- File is a sequence of memory locations

- Starting address of file is stored in the memory

locationimmediately after the program - If file character equals input character,

increment counter - End of file is indicated by a special ASCII

value EOT (x04) - At the end, print the number of characters and

halt(assume there will be less than 10

occurrences of the character) - A special character used to indicate the end of a

sequence is often called a sentinel. - Useful when you dont know ahead of time how many

times to execute a loop.

78

Flow Chart

An Example

79

Program (1 of 2)

An Example

80

Program (2 of 2)

An Example

81

LC-3 Data PathRevisited

Filled arrow info to be processed. Unfilled

arrow control signal.

82

Data Path Components

- Global bus

- special set of wires that carry a 16-bit signal

to many components - inputs to the bus are tri-state devices,that

only place a signal on the bus when they are

enabled - only one (16-bit) signal should be enabled at any

time - control unit decides which signal drives the

bus - any number of components can read the bus

- register only captures bus data if it is

write-enabled by the control unit - Memory

- Control and data registers for memory and I/O

devices - memory MAR, MDR (also control signal for

read/write)

83

Data Path Components

- ALU

- Accepts inputs from register fileand from

sign-extended bits from IR (immediate field). - Output goes to bus.

- used by condition code logic, register file,

memory - Register File

- Two read addresses (SR1, SR2), one write address

(DR) - Input from bus

- result of ALU operation or memory read

- Two 16-bit outputs

- used by ALU, PC, memory address

- data for store instructions passes through ALU

84

Data Path Components

- PC and PCMUX

- Three inputs to PC, controlled by PCMUX

- PC1 FETCH stage

- Address adder BR, JMP

- bus TRAP (discussed later)

- MAR and MARMUX

- Two inputs to MAR, controlled by MARMUX

- Address adder LD/ST, LDR/STR

- Zero-extended IR70 -- TRAP (discussed later)

85

Data Path Components

- Condition Code Logic

- Looks at value on bus and generates N, Z, P

signals - Registers set only when control unit enables them

(LD.CC) - only certain instructions set the codes(ADD,

AND, NOT, LD, LDI, LDR, LEA) - Control Unit Finite State Machine

- On each machine cycle, changes control signals

for next phaseof instruction processing - who drives the bus? (GatePC, GateALU, )

- which registers are write enabled? (LD.IR,

LD.REG, ) - which operation should ALU perform? (ALUK)

- Logic includes decoder for opcode, etc.