CSCE 613 PowerPoint PPT Presentation

Title: CSCE 613

1

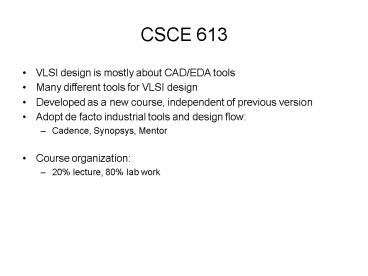

CSCE 613

- VLSI design is mostly about CAD/EDA tools

- Many different tools for VLSI design

- Developed as a new course, independent of

previous version - Adopt de facto industrial tools and design flow

- Cadence, Synopsys, Mentor

- Course organization

- 20 lecture, 80 lab work

2

Information

- Catalog Description

- 613 - Fundamentals of VLSI Chip Design. (3)

(Prereq ELEC 371) Design of VLSI circuits,

including standard processes, circuit design,

layout, and CAD tools. Lecture and guided design

projects. - Textbook(s) and Other Required Material

- Neil H.E. Weste, David Harris, CMOS VLSI Design

A Circuits and Systems Perspective 3rd Ed.,

Addison Wesley 2006, ISBN 0321149017. - Reference http//www.cse.sc.edu/jbakos/613

(tutorials and additional instruction for lab

work)

3

Outcomes

- Course Outcomes

- After completing this course students should be

able to - Design CMOS logic using MOSFET devices, perform

circuit-level simulation of CMOS logic gates to

determine logic delay - Characterize MOSFET devices for I-V behavior,

gate and parasitic capacitance, and effective

resistance - Design a library of standard logic, driver, and

memory cells using schematic capture, layout,

DRC, extraction, layout-vs-schematic, library

characterization, and abstract generation - Design large-scale digital logic system using

VHDL behavioral design and simulation - Synthesize, place-and-route, and generate cell

and interconnect delay models for VHDL designs

using their custom-designed standard cell library

4

Topics

- Topics Covered

- CAD/EDA design flow (spanning circuit-level,

logic-level, and system-level) - Design methodologies and techniques

- Logic delay and delay models

- CMOS logic design

- MOSFET semiconductor theory

- Circuit simulation

- Logic verification

- Standard cell library design

- Managing design complexity of large-scale digital

systems - Behavioral design of arithmetic logic unit

(bit-wise logic, shifting, rotating, fast

addition, fast subtraction, multiplication,

division)

5

Course Structure

- 3 weeks of lectures covering semiconductor

theory, MOSFET characterization, library design,

VHDL design, and CMOS design - One written homework assignment CMOS design

fundamentals - 3 labs covering MOSFET and CMOS gate

characterization using circuit simulation

techniques - Lab 1 CMOS gate delay

- Lab 2 MOSFET I-V behavior

- Lab 3 gate and diffusion capacitance

characterization - 1 lab where the students design and characterize

a standard cell library (Lab 4) - 1 lab where the students design a 16-bit

accumulator-based ALU (add, subtract, multiply,

divide, shifting, rotating, bit-wise logical) - Final project demoed during finals week

6

Webpage

- Webpage contains

- 10 fully custom-designed tutorials for HDL -gt to

silicon design flow

7

Course Schedule

- 3 weeks of lecture, homework and reading

assignments - 1.5 weeks of IC design tutorial work

- 1 week for Lab 1

- 2 weeks for Lab 2

- 2 weeks for Lab 3

- 2 weeks for Lab 4

- 1.5 weeks of VHDL lectures

- 2 weeks for synthesis / place-and-route tutorials

- 2 weeks for project work

8

Student Makeup, Performance

- Fall 2006

- 4 CE students, 10 graduate students (one from EE)

9

Grade Distribution