Statement of the Problem PowerPoint PPT Presentation

1 / 19

Title: Statement of the Problem

1

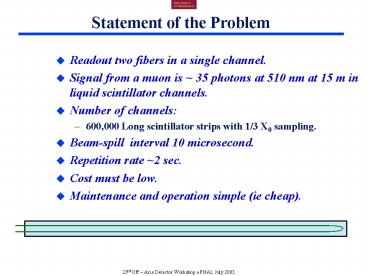

Statement of the Problem

- Readout two fibers in a single channel.

- Signal from a muon is 35 photons at 510 nm at

15 m in liquid scintillator channels. - Number of channels

- 600,000 Long scintillator strips with 1/3 X0

sampling. - Beam-spill interval 10 microsecond.

- Repetition rate 2 sec.

- Cost must be low.

- Maintenance and operation simple (ie cheap).

2

Spectrum

Attenuation 1m to 8m

At 510 nm signal drops by 5

At 540 nm signal drops by 2

PMTs prefer it blue.

For L large, the attenuation length of light at

500 nm is 10m determined by the plastic in the

fiber not the internal reflections. This is

measured with a PMT.

3

Off-Axis Application

- APD array

- Same junction as in CMS APD.

- Isolation between pixels made with diffusion and

implantations.

A dime (10)

Two 16-channel arrays

Operating characteristics are the same as the CMS

APD.

4

APD Operation I

Electrons generated by the incident light are

multiplied in the high field region at the

junction.

5

APD Operation II

- APDs are temperature dependent.

- Gain (M) variation is

- The gain increases as the temperature decreases.

- The Gain is voltage dependent

- The value of the voltage dependence is determined

by the junction structure. - The gain is determined uniquely by the applied

voltage and the temperature. If you control these

the gain is fixed. - Calibration of the APD is a simple matter.

Hamamatsu figure

Hamamatsu figure

6

Quantum Efficiency

- QE sits is around 85. at spectral peak

and is repeatable.

Measured in CMS APD.

7

Excess Noise Factor

- Excess noise Factor increases linearly with gain.

F k M 2 Þ k 0.0055 Excess noise factor F

2.5 at M 100 and 3.1 at M 200. Variance of

multiplication sM2 (F-1)

Measured in CMS APD.

8

Gain measurements on a single pixel.

At M 100 DV 26 V.

DV

All pixels show same behavior

9

Gain Distribution

This uniformity is consistent with the device

uniformity we have seen on the CMS APDs

10

Pixel Isolation

- Scanning array with spot of 520 nm light 0.1 mm

steps. - Pixels are uniform.

- Pixels are well isolated.

11

Costs

- Pixel size is 1.6 x 1.6 mm2.

- Use bare die (Protected with Si3N4 coating not

epoxy) just like in silicon trackers. - Price in quantities of 500,000 channels - 2.65 -

2.75 ea. - Price in quantities of 1,500,000 channels - 2.00

- 2.10 ea.

The prices were quoted before the dollar took a

nose-dive

12

Application

- Low Gain 100 means that electronics noise is

critical. - Signal

- minimum signal considered 25 photo-electrons for

a 15m long liquid scintillator with a doubled 0.7

mm diameter fiber readout. - Use double correlation technique to detect signal

used in one Fermilab chip (MASDA).1998 Fermilab

design. - Noise sources

- Shot noise from thermal generation at the

junction (IB) - Johnson noise at amplifier input. (C2R)

- Amplification noise in APD avalanche. (F)

- Johnson noise from the detector series current is

suppressed by the gain.

13

Signal

Signals estimated by KR for MINOS scintillator

strips .

Use 25 PEs as target minimum signal.

These figures have been changed with scintillator

design. There are rumours of 55 pes.

14

Noise

Noise Sources

Fluctuations on signal

Fluctuations on thermal electrons

Excess noise factor Gaussian Variance F - 1

Johnson noise at the pre-amp input Gaussian.

Preamp

ADC

Refer all fluctuations back to input signal.

15

Addition of Noise

Poisson Statistics

Excess Noise Factor

Preamp

ADC

16

Noise.

- Use as input the MASDA chip parameters.

- This is an old chip designed for the readout of

amorphous silicon TFTs high capacitance gt70pf. - Uses double correlated sampling.

- 128-channels.

- Provides proof-of-principle for electronics.

- Measured noise with a 10 pF capacitance is 330

nsec for a shaping time of 360 nsec.

Leon will talk about results obtained with this.

17

Basic Front-End Readout.

- Design for pulsed beam only.

- Use MASDA Front-end structure.

- Integrating capacitor, with slow discharge time.

- Use double correlated sampling as in MASDA.

- Shaping-time 250nsec.

- Sample integrating capacitor every 500 nsec.

- Store output in SCA.

- After beam pulse digitize all signals seperated

by 1000 nsec. - Final ASIC MASDA PA SCA ( ADC?)

18

Timing

2 Mhz clock

A

B

C

D

E

F

H

I

J

K

Digitize C-A, D-B, E-C, etc. or DE-AB,

EF-BC, etc.

19

APD module

- Front-end readout module requirements

- 64 Fiber connection.

- APD basic building block is 2 x 8 array.

- TE cooler.

- ASIC.

- Cockroft Walton.

- ADC maybe on ASIC.

- FPGA. Data processing and store, clock

regeneration. - Trigger output.

- LV power input.

- Design whole assembly for external manufacture.

- Significant cost-savings by good manufacturing

design.

20

Questions.

- Fiber-APD interface.

- DAQ.

- Clock synchronization.

- Module Manufacture approaches.

- ADC on or off chip.

- Who does what in the coming months.

- Milestones and benchmarks.

- What is success (failure)?

Many customers for APD modules who want to learn

about this technology.

21

Cost Estimate.

- Assumptions

- 64-channel fibers-APD modules.

- Cooling with a single stage Thermal Electric

cooler. (Peltier). - Cool only APD (0.2 mW) to 10C. Not electronics.

- HV (400 V) supplied by a single Cockroft-Walton

supply (being designed at Fermilab). 1/module. - Readout concept.

- 64-channel ASIC Charge in/Bits out.

- Continuous charge integration.

- Divide spill into 100 nsec intervals.

- Store integrator output values on capacitors

- One capacitor for each interval. (Like SVX4).

- Convert charge on caps with one on-chip 10-bit

ADC. - Control Logic (FPGA)

- Generates trigger bit.

- Sends all data after trigger accept to event

concentrator (1024 -channels). - Resets ASIC.

- Send data to DAQ on commercial fiber optic link

1/1024 channels.

22

Cost Estimate

System costs were estimated by Ray Yarema all

costs are fully burdened and include engineering,

prototyping, fabrication and testing for

1,000,000 yielded channels.

- Cockroft-Walton

- Chip cost 8.70

- Chip area 12 mm2, 10 wafers masks -- 50k (55k

for masks). - Testing -- 136,000.

- Other on board components. 7.00

- Cost per 64 channels 15.70 (0.25/channel.).

- APD readout chip.

- Chip cost 33.79.

- 48 mm2 size total area 750,000 mm2, 40 wafers

(200k). - Testing - 50/die.

- Cost per 64 channels 33.79 (0.53/channel.).

23

Cost Estimate

- Board costs

- Circuit board cost 3.00 (15,000 4-layer 2 x

4 boards) - TE cooler 5.00 (Just the junction - Catalog)

- Thermocouples 2.00

- Small FPGA (400 NAND gates) 5.00

- Four 16 channel APDs 64 x 2.50 160

- C-W chip and support parts 15.70

- APD readout chip 33.79

- Other parts 2.00

- Board Assembly 5.00

- Production board tester 2.00 (?)

- Board test and repair 5.00 (?)

- Total estimated readout cost 3.73 /channel

including APD. - Add 25 contingency.

Cost per channel including the APD and 25

contingency 4.65.