Active System Area Networks (ASAN) - PowerPoint PPT Presentation

1 / 1

Title:

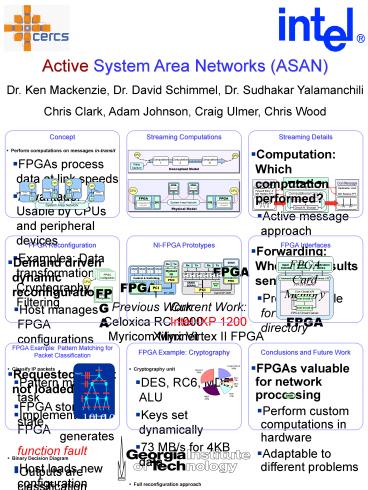

Active System Area Networks (ASAN)

Description:

Advantage: Usable by CPUs and peripheral devices ... GRIM. NI. FPGA. System Area Network. NI. Computational. Circuit N. FPGA. CPU. NI. FPGA. NI. FPGA ... – PowerPoint PPT presentation

Number of Views:22

Avg rating:3.0/5.0

Title: Active System Area Networks (ASAN)

1

Active System Area Networks (ASAN) Dr. Ken

Mackenzie, Dr. David Schimmel, Dr. Sudhakar

Yalamanchili Chris Clark, Adam Johnson, Craig

Ulmer, Chris Wood

Concept

Streaming Computations

Streaming Details

- Computation Which computation performed?

- Active message approach

- Forwarding Where are results sent?

- Programmable forwarding directory

- Perform computations on messages in-transit

- FPGAs process data at link speeds

- Advantage Usable by CPUs and peripheral devices

- Examples Data transformations, Cryptography,

Filtering

Conceptual Model

FPGA

In Message

Out Message

Forwarding Directory

Destination FPGA Forward Entry X AM Perform FFT

Destination Host AM Receive FFT

Physical Model

FPGA Reconfiguration

NI-FPGA Prototypes

FPGA Interfaces

- Demand driven dynamic reconfiguration

- Host manages FPGA configurations

- Requested circuit not loaded?

- FPGA stores state, generates function fault

- Host loads new configuration

- FPGA loads state, restarts

- Currently Full FPGA reconfiguration

- Research Partial run-time reconfiguration

FPGA Card Memory

FPGA Control

RC-1000

Previous Work Celoxica RC-1000 Myricom Myrinet

Current Work Intel IXP 1200 Xilinx Virtex II FPGA

FPGA Circuit Canvas

FPGA

FPGA Example Cryptography

Conclusions and Future Work

FPGA Example Pattern Matching for Packet

Classification

- FPGAs valuable for network processing

- Perform custom computations in hardware

- Adaptable to different problems

- ASAN allows computations to take place in network

- Processing in NI and peripheral devices

- Powered by communication library

- Future work

- Partial FPGA reconfiguration mechanisms

- Selectable computation target (Host, NI, or FPGA)

- Transition to IXP based Gigabit Ethernet

- Classify IP packets

- Pattern matching task

- Implement in FPGA

- Binary Decision Diagram

- Outputs are classification

- Map BDD to FPGA gates

- Muxes and registers

- Cryptography unit

- DES, RC6, MD5, ALU

- Keys set dynamically

- 73 MB/s for 4KB data

- Full reconfiguration approach

- Configure time 90 ms

- Possible to create optimized key-specific

configurations

Inputs

1

0

1

0

1

0

Classifications