MIPS Datapath PowerPoint PPT Presentation

Title: MIPS Datapath

1

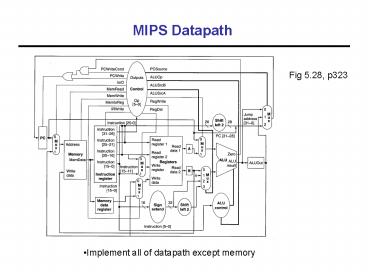

MIPS Datapath

Fig 5.28, p323

- Implement all of datapath except memory

2

System Block Diagram

- MemDataIn is the input port

- AddressOut and WriteDataOut are output ports

- Reset clears regfile and all registers

- Ignore memory control signals for now

3

Implementation/Test Process

- IF, ID, EX, MEM, WB

- Send data to each stage through previous stages

- Directly observe output of a stage to check

results

4

Simulating an Instruction

- Testing is performed by simulating instructions

- Simulate an instruction by

- 1. Applying the correct control sequence

- 2. Applying the instruction to MemDataIn during

the first clock cycle - Testbench needs to apply these signals to the

datapath inputs

5

Control Sequence

- Fig 5.38, p339

- You will change these signals in your testbench

for this lab - Ignore MemRead and MemWrite

6

Testing Stages

IF stage is all logic driving instruction reg and

memory data reg - Memory is external so this

stage is simple - Test this stage by loading the

registers ID stage drives registers A and B -

Test by reading register file (ex. OP x, y,

z) - Initialize register file contents

first EX stage drives ALUOut - Test by

performing OP x, y, z - Initial y, z, check

x MEM stage drives AddressOut, WriteDataOut -

Test with LW, SW, check outputs WB stage drives

register file - Test with LW x, 100(y), check

x

PowerShow.com is a leading presentation sharing website. It has millions of presentations already uploaded and available with 1,000s more being uploaded by its users every day. Whatever your area of interest, here you’ll be able to find and view presentations you’ll love and possibly download. And, best of all, it is completely free and easy to use.

You might even have a presentation you’d like to share with others. If so, just upload it to PowerShow.com. We’ll convert it to an HTML5 slideshow that includes all the media types you’ve already added: audio, video, music, pictures, animations and transition effects. Then you can share it with your target audience as well as PowerShow.com’s millions of monthly visitors. And, again, it’s all free.

About the Developers

PowerShow.com is brought to you by CrystalGraphics, the award-winning developer and market-leading publisher of rich-media enhancement products for presentations. Our product offerings include millions of PowerPoint templates, diagrams, animated 3D characters and more.