9U FEDv1 New Production PowerPoint PPT Presentation

Title: 9U FEDv1 New Production

1

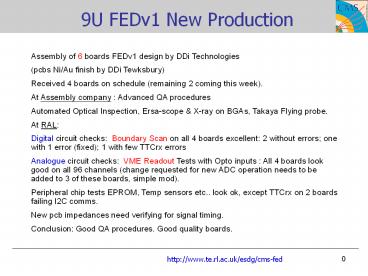

9U FEDv1 New Production

Assembly of 6 boards FEDv1 design by DDi

Technologies (pcbs Ni/Au finish by DDi

Tewksbury) Received 4 boards on schedule

(remaining 2 coming this week). At Assembly

company Advanced QA procedures Automated

Optical Inspection, Ersa-scope X-ray on BGAs,

Takaya Flying probe. At RAL Digital circuit

checks Boundary Scan on all 4 boards excellent

2 without errors one with 1 error (fixed) 1

with few TTCrx errors Analogue circuit checks

VME Readout Tests with Opto inputs All 4 boards

look good on all 96 channels (change requested

for new ADC operation needs to be added to 3 of

these boards, simple mod). Peripheral chip tests

EPROM, Temp sensors etc.. look ok, except TTCrx

on 2 boards failing I2C comms. New pcb impedances

need verifying for signal timing. Conclusion

Good QA procedures. Good quality boards.

2

FEDv1 Firmware

- Major Activities to verify FEDv1 Design

- Done

- Front-End FPGA Algorithms Baseline algorithms

(flat CM) now tested and working. - S-LINK Test fast readout logic using DAQ

FEDKit. 100kHz random trigger data transfers now

working reliably 64 bits _at_ 80MHz. BERs being

measured. - SPY Channel Copy of raw data via VME for

checking zero suppression is working. - Peripherals EPROM for holding permanent data

working. Temperature Voltage monitoring devices

working. - FPGA in-situ reprogramming Compact Flash card

holding permanent FPGA configurations can now be

re-programmed in-situ over network. - To do...

- TTCrx ChanB Transfers from APVE under test.

3

CMS Tracker FED Firmware Status

15th March 2004

System ACE

EPROM

VME FPGA

Ed-gtSaeed

DAC

EPROM

Opto Rx

Temp

System ACE

ADC

DAC

VME Bus

Opto Rx

Temp

VME

ADC

Clocks

I2C

Clocks

Serial Comms

Regs

Clocks

Serial Comms

Regs

Data

Serial Comms

VME LINK

Input

Spy

Data

Header Mode

Header Mode

Cluster Mode

Input

Ed-gtSaeed

FIFOs

Scope Mode

Output

DELAY FPGA x 3 x 8

BE FPGA

Saeed

Scope Mode

Serial Comms

VME Link

Regs

External Devices

FE FPGA x 8

Saeed

To be Implemented

S-LINK

S-LINK

Control

Headers

Under Simulation

Throttle

TCS

Input

Under Test on FED

QDR Write

QDR Read

TTC chanA

TTCrx

Data Readout

Saeed, Ivan

Working on FED

Chan B

QDRs

Controls

Ed, John

FEDv2

4

CMS Tracker FED Firmware Status

4th November 2003

System ACE

EPROM

VME FPGA

Ed-gtSaeed

DAC

EPROM

Opto Rx

Temp

System ACE

ADC

DAC

VME Bus

Opto Rx

Temp

VME

ADC

Clocks

I2C

Clocks

Serial Comms

Regs

Clocks

Serial Comms

Regs

Data

Serial Comms

VME LINK

Input

Spy

Data

Header Mode

Header Mode

Cluster Mode

Input

Ed-gtSaeed

FIFOs

Scope Mode

Output

DELAY FPGA x 3 x 8

BE FPGA

Saeed

Scope Mode

Serial Comms

VME Link

Regs

External Devices

FE FPGA x 8

Saeed

To be Implemented

S-LINK

S-LINK

Control

Headers

Under Simulation

Throttle

TCS

Input

Under Test on FED

QDR Write

QDR Read

TTC chanA

TTCrx

Data Readout

Saeed, Ivan

Working on FED

Chan B

QDRs

Controls

Ed, John

FEDv2