MUO PowerPoint PPT Presentation

1 / 18

Title: MUO

1

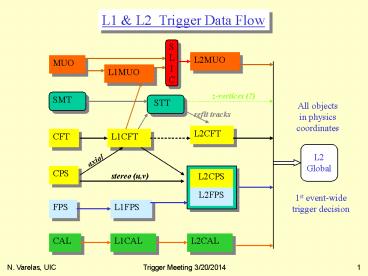

L1 L2 Trigger Data Flow

S L I C

L2MUO

MUO

L1MUO

z-vertices (?)

SMT

STT

All objects in physics coordinates

refit tracks

L2CFT

CFT

L1CFT

L2 Global

axial

CPS

L2CPS

stereo (u,v)

L2FPS

1st event-wide trigger decision

FPS

L1FPS

CAL

L1CAL

L2CAL

2

DØ Level-2

3

Example L2 Crate Calorimeter

MCH1

Optical Signal inputs from L1 4 2 4

MagicBus

M P M - B I T 3

V B D

F I C

F I C

F I C

four MBT channels

to L3

six MBT channels

All Hotlink connections are single channel UTP

cables on Front Pannels MBT (hotlinks) outputs L2

objects to Global MBT receiver

4

Example L2 Crate Muon

Coax. (SMB cable) inputs from FE L1 into 14

CICs in dedicated crate

MCH3

MagicBus

double channel UTP cables to SLICs

M P M - B I T 3

V B D

S L I C

S L I C

S L I C

M B T

M B T

S F O

eleven total

pilot

assist.

SCL

eleven MBT channels

to L3

to Global

All Hotlink connections are single channel UTP

cables on Front Pannels MBT (hotlinks) outputs L2

objects to Global MBT receiver

5

L2 Crate Locations

6

L2 to Test Stand Connections

Patch panels have identical maps

MCH3 Muon

Source Inputs

SCL (Hub) 1 (?)

SCL 6

CAL 10

PSH 12

CTT 16

MUO 18

Global 10

L1 Mask 1

SLIC 14

Total 88

()

Patch Panel

Permanent cabling

MCH2 STT CTT , PS

FCH2 Test Stand

MBT Channels

MCH1 CAL Global

Image Patch Panel

SLIC Channels

Permanent cabling between MCH and T.Stand is

open ended at MCH for minimal noise. Cables are

bundled acc. to table above. Connect as needed

() The only non-hotlink connection in

P.Panel

obs window is 45x45 cm conn.2x3cm

7

Status of Installation

- Racks, Crates, Power, Cooling (MCH and FCH)

- Except muon CIC crate (April?)

- Almost all Cabling in place

- building muon pigtails

- some remaining cabling at the test stand

- cabling for L3 readout

- MCH-FCH Window Patch Panel

- not installed yet

- need to build 2nd patch panel for the test stand

- L2 trigger mask to L2HWFW (soon?)

- L1HWFW to L2Global (via FIC) (soon?)

- Monitoring of Alphas by L1 Scalers

- ORCs in April

8

Status of L2 Cards

- FIC

- All cards are done

- BIST errors identified last Fall have been fixed

at SACLAY by replacing mismatched signal path

with UTP cable - One modified FIC worked fine in BIST mode

- Cards are currently at UIC to do the wire mods

- MBT

- All cards at UMd testing in progress

- 3 production cards at D0 (3/13/01)

- commissioning of Alpha-MBT communication in

progress - VHDL firmware is 95 done

- Programmed I/O, Broadcast, Monitoring

- SCL handling (April)

9

Status of L2 Cards contd

- SLIC

- All cards are here

- Its a software problem now

- Basic operating system done

- CIC

- BIST tests with the two pre-production boards

were completed last week - lt1x10-12 BER with 40 Forward-Central Sci/MDT

channels - of these channels 1 found dead and 2 gave 1x10-9

BER (consistent with L3 BIST testing) - suspect

problems with Mu FE cable/driver - must test the remaining 100 PDT channels with

BIST - board released for production last Monday

(3/12/01) - expected delivery of 18 (tested) boards by

mid-May - needed only by muon system

10

Status of L2 Cards contd

- SFO

- two pre-production boards pass all tests

- released for production last week

- expected delivery of 28 tested boards by mid-May

- needed by muon system and for test stand

- Alpha

- 2 pre-productions (1 CDF) worked within 1 week

almost a year ago - 24 production boards delivered on Sep 13, 2000

- zero boards worked within 1 week!

11

Alpha Board

12

21172 Chipset

13

Status of L2 Cards contd

- Alpha contd

- Many production errors are to blame

- broken vias

- small finished sizes

- boards sat 6 months from preprod to final

production - aging of OPC coat decreases solderability

- OPC is reactive and can thin vias

- popcorning of Universe BGA (almost 100 failure)

- recently confirmed by failure analysis

- delamination of the CIA BGA (gt63 failure)

- recently confirmed by failure analysis

- additional concern bad CIA chips - wire bond

cross over - bad quality control

- rotated chips, missing components, no

connectivity to some components, marginal solder

coverage to some R/Cs

14

Status of L2 Cards contd

- Alpha contd

- currently we have 9 functional boards (2 pre-prod

7 prod) - total number is limited by the number of bad-CIA

boards - replacing the CIA has been very adventurous BGA

sits in the middle of a 9U board much better

repair yield with Universe BGA - long term reliability has been recently tested

for almost all boards encouraging results,

however, there are concerns with board

lifetime/handling - some Mbus problems (PIO/DMA) make testing of

board difficult - Bob, Stephen, and Drew are currently at D0

debugging these remaining features hopefully all

problems are fixable in firmware

15

Status of L2 Cards contd

- Alpha contd

- Assembly of 12 additional boards last shot

- CIA will be socketed due to concerns of bad chips

in hand - buying 5 more sockets to fix for existing Alphas

- 4 weeks lead time PO in progress

- mods to the production layout are completed

(Stephen, UM/CDF) Johnny Green is reviewing the

changes (this week?) - mods include dogbone widths under BGA, wire

mods, L3 cache, re-route R/Cs near the CIA for

socket installation - board vendor has been selected PO is ready

- turnaround time is 5-10 days

- use white-tin plating instead of OPC

- bake BGAs before installation

- expect prototype board gt4 weeks after PCBs with

remaining boards 4 weeks after that - realistically around July for tested boards

- Beta design proceeds full speed ahead (Orsay,

UMd, UVA)

16

Online Software Status

- Alpha

- Much of structural software exists in simulation

- Control/data flow for preprocessor and global

- Draft drivers/setup for MBT and event loop

March/April - Some alpha firmware problems?

- SCL_INIT, and DAQ interface

- VME driver, buffer allocation Done

- VBD/L3 readout beginning DONE (3/14)!

- Error logging and beginnings of monitoring

Done - Downloading, release to Worker 95 done

- Admin/Worker control data flow May

- SLIC

- Basic operating system in place

- Code moving to CVS testing download scheme

- VME drivers written March

17

Algorithms in Simulator

- Mu L1 seeds DSP Segment Finders,

- Central, Fwd track assembly code April

- CTT

- not tested yet

- PS

- CPS more work needed

- FPS written April?

- Cal

- e Run 1B L1.5

- j merge needs work

- MET L1

- Global

- e(cal,cps), j(cal) (e fps, ctt ready)

- Ht, MET (mass)

- Mu(with ctt) Apr/May?

- STT April?

?

18

Time Line

15-Mar 6-11 Alphas Available

? 15-Mar MBT's on Site ? 1-Apr

MBT-Alpha-VBD Data Flow ? Apr L2 Muon

Software Integrated May

2Alpha/MBT/VBD Integration May

Begin Cal/Muon/Global Ind. Integration May

Muon I/O Cards (CIC/SFO's) Jun

Global/Cal/Muon in L3/DAQ Jul Twelve

Additional alphas (repairprod) Jul Start

PS/CTT