I. Structure of AC Plasma Display Panel - PowerPoint PPT Presentation

Title:

I. Structure of AC Plasma Display Panel

Description:

Power Loss of Sustain Circuit 4. ... Address Buffer Board (Lower) Power Supply Board Logic Board Image ... Driver Board Y-BRD X-BRD Scan Buffer SMPS Logic Address ... – PowerPoint PPT presentation

Number of Views:118

Avg rating:3.0/5.0

Title: I. Structure of AC Plasma Display Panel

1

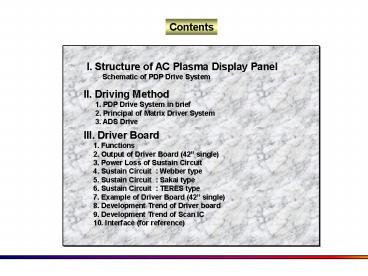

Contents

I. Structure of AC Plasma Display Panel

Schematic of PDP Drive System

II. Driving Method 1. PDP Drive System in

brief 2. Principal of Matrix Driver System

3. ADS Drive

III. Driver Board 1. Functions 2.

Output of Driver Board (42 single) 3. Power

Loss of Sustain Circuit 4. Sustain Circuit

Webber type 5. Sustain Circuit Sakai

type 6. Sustain Circuit TERES type

7. Example of Driver Board (42 single) 8.

Development Trend of Driver board 9.

Development Trend of Scan IC 10. Interface

(for reference)

2

I. Structure of AC Plasma Display Panel

3

I. Structure of AC Plasma Display Panel

Schematic of PDP Drive System

4

II. Driving Method

1. Principal of Matrix Driver System

5

2. Driving Method

Principal of Matrix Driver System

6

II. Driving Method

2. Structure of ADS Drive Method

Gray scale is displayed by s/w On of specific

SF(sub field) in 1TV frame(field time).

7

II. Driving Method

3. Feature of ADS Drive Pulse

- (Terminology)

- Reset Elimination of Sustain discharge

/ - Formation of Address

discharges condition - Address Selection of ON/OFF Cell

- Sustain Display real picture through

Sustain discharge - Time In case of Dual Scan (480 scan

line), 1 Frame (16.67msec) are organized - Reset 15 20, Address 40

50 and Sustain 35 40.

8

Address Operation

In order to display picture, select the cells.

9

Sustain operation

Display cells through strong Sustain discharge.

10

Erase / Reset

Elimination for next image (generate Display

discharge)

11

III. Driver Board

1. Functions

Disposition of Boards

Address Buffer Board (upper)

Power Supply Board

Logic Board

Y Electrode

X Electrode

Image Processing Board

X-Bd

Y-Bd

Address Buffer Board (Lower)

Scan-Bd

Sustain pulse generation Reset pulse

generation Scanning operation

Basic signal protection Short circuit protection

Main functions

12

III. Driver Board

Y- Board Power Signal Flow

Switch On / Off

Reset / Scan Wave

Reset / Scan Volts

AC Power

Switch On / Off

Sustain Volts

Sustain Wave

Filter

Logic Volts

Scan Buffer

Capacitor

FET Drive Volts

Y - Electrode

Logic Signal

Logic Board

13

III. Driver Board

X- Board Power Signal Flow

Switch ON/OFF

X-bias

X-bias Volts

AC Power

Switch ON/OFF

Sustain Volts

Sustain Wave

Filter

Logic Volts

Capacitor

FET Drive Volts

Y - Electrode

Logic Board

Logic Signal

14

III. Driver Board

2. Output of Driver Board (42 Single)

Sustain Discharge Luminescence part

Addressing gt Address period is long

- Reset

- Ramp Reset

- (weak discharge reset)

- Contrast, operation margin,

- expanded production rate

15

III. Driver Board

2. Output of Driver Board(42 Dual Scan)

Reference

Dual Scan (Address period is short)

LOG Reset Wave in use

- The point of view on Driver board, Dual Scan is

same structure with Single Scan except the

circuit - of Reset Wave output.

16

III. Driver Board

3. Power Loss of Sustain circuit

PDP Structure

Basic sustain circuit

PDP panel

17

III. Driver Board

PDP

Discharge of Capacity load

Heat loss

Heat loss

Power loss

About 120 Watts in case of 42inch panel

C panel capacitance V sustain voltage f

average frequency

18

III. Driver Board

4. Sustain Circuit Webber type

Y-Board

X-Board

Panel

Sustain circuit

Energys Recovery circuit

Energys Recovery circuit

- Operation performance of this circuit is

good. (compatible with most Waves) - Overall efficiency is high.

- (On the usage of LC Resonance circuit,

switching loss should be small.) - Simple operation and organization. Operation is

stable. - Production enterprise with Webber type

-

Matsushita, Fujits, Pioneer, LG, Samsung

Characteristics

19

III. Driver Board

Hard switching generation

1. Rising period

Ys,Xg

Yr,Xg

Yf,Xg

Yg,Xg

2. Vs - Sustain period

Sustain Wave

Y

X

Light Wave

Observation Wave

20

III. Driver Board

Hard switching generation

3. Falling period

Ys,Xg

Yf,Xg

Yr,Xg

Yg,Xg

4. GND period

Sustain Wave

Y

X

Light Wave

Observation Wave

21

III. Driver Board

5. Sustain Circuit Sakai type

Y-Board

X-Board

Panel

Energy Recovery circuit

- Operation performance of this circuit is low.

- (It is not proper to recover the energy except

Sustain part.) - Overall efficiency is high.

- (On the usage of LC Resonance circuit,

switching loss should be small.) - Simple operation and organization. Operation is

stable. - Production enterprise with Sakai type NEC

Characteristics

22

III. Driver Board

Hard switching generation

1. Y rising X falling period

Sa

Ys,Xg

Xs,Yg

Sb

Sustain Wave

Ys,Xg

Yr,Xg

Yf,Xg

Yg,Xg

2. Sustain period

X

Y

Observation Wave

23

III. Driver Board

Hard switching generation

3. X rising Y falling period

Sa

Ys,Xg

Xs,Yg

Sb

Sustain Wave

Ys,Xg

4. Sustain period

X

Y

Observation Wave

24

III. Driver Board

6. Sustain Circuit TERES type

Panel

Charge pump??

- TERES type hold a patent right for the structure

of Sustain circuit. - It is advantage of low price. (low voltage part

in use) - Complicated operation and organization.

- It should be added ERC circuit like Sakai type

or Webber type. - Production enterprise with TERES type FHP

Characteristics

25

III. Driver Board

Sustain path

Vy

Vx

Charge pump path

Vy

Vx

Internal voltages of Device ½ comparing with

the other type Performance same as the

other type Cost profitable

comparing with the other type Application

It is not compatible with every Waves

( swing ,- by turns)

Sustain path

Charge pump path

26

III. Driver Board

7. Example of Driver Board ( 42 single )

Ysc

Dyvs

- ERC circuit (Yr,Yf,Dyys,Dyr,Dyf,Dyg)

- gt Energy recovery

- Sustain circuit (Ys, Yg)

- gt Sustain Discharge

- Reset circuit (Yrr, Yfr)

- gt Elimination of Panel

- Path circuit (Yp, Ysp)

- gt Formation of Main Path

- Scan circui t(Ysc)

- gt Scan Bias

Yrr

Ys

Yp

Dyr

Yr

Dyf

Yg

Yp

Ysp

Yf

Dyg

Yfr

Y-Board

27

III. Driver Board

Xrr

- ERC circuit (Xr, Xf, Dxvs, Dxr, Dxf, Dxg)

- gt Energy recovery

Dxvs

Xf

- Sustain circuit (Xs, Xg)

- gt Sustain Discharge

Xs

Dxf

- Reset circuit (Xrr)

- gt Elimination of Panel

Xr

Dyf

Dxr

Xg

Dxg

X-Board

28

III. Driver Board

42 single

Scan Buffer

Y-BRD

X-BRD

SMPS

Logic

Address Buffer

29

III. Driver Board

50 Dual

Scan Buffer

Address Buffer

Y-BRD

X-BRD

SMPS

Logic

Address Buffer

The Load of Driver Board(50) is about 1.5

times bigger than 42s.

30

III. Driver Board

50 Dual

Clamping Diode

Clamping Diode

Ysc

Xf

Xs

Ys

Yr

Yp

Ysp

Xrr

Yf

Xr

Yg

Xg

Yrr

Yfr

Blocking Diode

31

III. Driver Board

Circuit Block Diagram

Path circuit(Yp, Ysp)

Scan circuit(Ysc)

Sustain circuit (Xs, Xg)

Sustain circuit (Ys, Yg)

Reset circuit (Yrr, Yfr, Xrr)

ERC circuit (Yr, Yf, Dyvs, Dyr, Dyf, Dyg)

ERC circuit (Xr, Xf, Dxvs, Dxr, Dxf, Dxg)

32

III. Driver Board

Operations(Sustain part)

(2)

(1)

(4)

(3)

Yp, Ysp ON

33

III. Driver Board

Operations (Reset part)

(2)

(1),(4)

(2)

Regarding rising points and falling points of

Ramp Wave, use Sustain operations.

34

III. Driver Board

Operations (Scan part)

35

III. Driver Board

Operations (Scan part)

768 line

scan

tt0

tt1

480 line

tt2

tt3

GND

tt0

tt1

Address

tt2

tt3

36

III. Driver Board

Path Diode

Path Diode

Discharge Current Ipk 120A-150A pulse width

1us??

Resonance Current Ipk 60-70A pulse width

300-400 ns

Parallel position of Switch

and Diode

X-BRD

Y-BRD

ERC S/W

Sustain S/W

Sustain Path S/W

ERC S/W

37

Examples of Operation Wave

III. Driver Board

Matsushita

Samsung

Matsushita

NEC

38

III. Driver Board

8. Development Trend of Driver board

- Improvement of Board efficiency and Design for

radiation of heat - Decline of Boards electric power consumption

and Operations - of Fanless motor for the

radiation. - Thickness ? Low depth

- Dignity elivation of the set

- Design for Low Cost

- a. Development of new part

- b. Change of Circuit Topology

- c. Design change in accordance with Operation

Wave change - Application of HIC (Hybrid Intergrated Circuit)

- PCB Size decline, Improvement of Production

process , - Development and Application trend

in each PDPs vendor - Development for self Operation type except a

patent right for Webber

39

III. Driver Board

9. Development Trend of Scan IC

- Scan IC / Address IC

- a. Low Coat

- Development of Low Voltage Address Operation

type - through change of Operation Wave

- ? Application of Low Voltage Driver

- b. High Speed

- Needs the Data processing quickly for the

- reduction of Address Cycle

- ? Speedy Data Shift Clock

40

III. Driver Board

10. Interface (for reference)

- Connection of the circuit output and Panel

- usage the FPC (Flexible Printed Circuit)

- Connection of Scan/Address Driver and Panel

- On the usage of FPC, Boards are connected

with - Panel electrode.

- a. Board Connector FPC Panel

- b. COB(FPC) Panel

- c. COF(FPC) Panel

- Trend changes to COB / COF type on

overall - PDP manufacturing vendors.

Example FPC(Flexible Printed Circuit)