Sequence detector PowerPoint PPT Presentation

1 / 25

Title: Sequence detector

1

Sequence detector

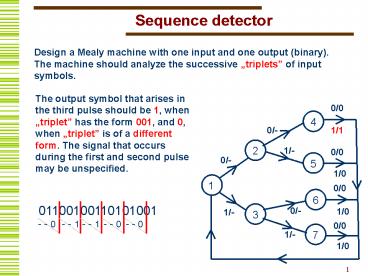

Design a Mealy machine with one input and one

output (binary). The machine should analyze the

successive triplets of input symbols.

The output symbol that arises in the third pulse

should be 1, when triplet has the form 001, and

0, when triplet is of a different form. The

signal that occurs during the first and second

pulse may be unspecified.

0/0

0/-

1/1

1/-

0/0

0/-

1/0

0/0

01100100110101001

0/-

1/0

1/-

- - 0

- - 1

- - 1

- - 0

- - 0

0/0

1/-

1/0

2

Sequence detector

1/-

0/-

3

Minimization of sequence detector

Many compatibles

We use incompatible pairs to find MCC, since

there is few of them, only two.

4

Minimization of sequence detector

Incompatible pairs we write as a Boolean

expression being a product of logic sums

In sequence detector the incompatibles are (2,

3) (4, 5).

Based on this we write the expression (2 ? 3) (4

? 5), which after multiplication obtains the

form (2 ? 3) (4 ? 5) 2 4 ? 2 5 ? 3 4 ? 3 5

Subtracting from set S 1, 2, 3, 4, 5 of all

states those sets of states that are written in

separate products we obtain the family of all MCC

1, 2, 3, 4, 5 2, 4 1, 3, 5 1, 2, 3, 4,

5 2, 5 1, 3, 4 1, 2, 3, 4, 5 3,

4 1, 2, 5 1, 2, 3, 4, 5 3, 5 1, 2,

4

5

Minimization of sequence detector

MCC 1, 3, 5, 1, 3, 4, 1, 2, 5, 1, 2, 4

Classes 1, 3, 5, 1, 2, 4 satisfy covering

condition,

Transition function for all MCC

But do not satisfy the closure condition the

next states 1,2,5 !

We add the class 1,2,5

Classes 1,3,5, 1, 2, 4, 1, 2, 5 satisfy

closure and covering conditions

Minimal automaton

6

...this is next realized

DGL6 Slides No. 17 to 23!

Whole synthesis process !

Formulation of sequence detector problem

7

Up/down mod. 5 binary counter

Counter operations

a up count up

b count down

c clear

ENCODING

8

Up/down counter

001 100 000 000

010 000 000 000

100 010 000 000

011 001 000 000

--- --- --- --- --- ---

--- --- --- --- ---

---

000 011 000 000

Q2Q1Q0

Q2Q1Q0

9

D Flip-Flops

For D type FFs Q D

Q2Q1Q0

D0

D1

D2

10

Up/down counter with D Flip-Flops

D2

D1

D0

11

Up/down counter with JK Flip-Flops

Table of function Q'

12

Counter with JK Flip-Flops

QQ J K 00 0 01 1 10 1 11 0

Q2

J2

K2

1

13

Up/down counter with JK Flip-Flops

Q1

J1

x1

K1

14

Up/down counter with JK Flip-Flops

Q0

J0

K0

1

15

Do not worry...

Sequential synthesis is a laborious process, in

which it is necessary to process huge tables

filled up with 0s and 1s

But do not worry! This process is fully

automated

16

Nie martwmy sie ...

the only activity of user

writing the state table in HDL

17

Specification of automata

Omitting details it is necessary to write state

table in HDL.

AHDL VHDL

Mapping

18

For example, our counter...

TABLE current

current next next

state input state output s,

v gt s, y

s0, B"00 gt s1, 0 s0, B"01

gt s4, 0 s0, B"1X gt

s0, 0 s1, B"00 gt s2,

0 s1, B"01 gt s0, 0

s1, B"1X gt s0, 0

s2, B"00 gt s3, 0 s2, B"01

gt s1, 0 s2, B"1X gt s0,

0 s3, B"00 gt s4,

0 s3, B"01 gt s2, 0

s3, B"1X gt s0, 0 s4, B"00

gt s0, 1 s4, B"01 gt s3,

1 s4, B"1X gt s0, 1

END TABLE

specified in AHDL,

then after ...

19

TABLE current

current next next

state input state output s,

v gt s, y

s0, B"00 gt s1, 0 s0, B"01

gt s4, 0 s0, B"1X gt

s0, 0 s1, B"00 gt s2,

0 s1, B"01 gt s0, 0

s1, B"1X gt s0, 0

s2, B"00 gt s3, 0 s2, B"01

gt s1, 0 s2, B"1X gt s0,

0 s3, B"00 gt s4,

0 s3, B"01 gt s2, 0

s3, B"1X gt s0, 0 s4, B"00

gt s0, 1 s4, B"01 gt s3,

1 s4, B"1X gt s0, 1

END TABLE

20

after starting compiler

...everything automatically will be calculated.

q0 _EQ001 !q0 q1 !X1 X2 q2

!X1 X2 !q0 !q2 !X1 !X2 q1

_EQ002 q2 !X1 X2 q0 q1

!X1 X2 !q0 q1 !q2 !X1 !X2

q0 !q1 !q2 !X1 !X2 q2 _EQ003

!q0 !q1 !q2 !X1 X2 q0

q1 !q2 !X1 !X2

21

Programmable Logic Devices

Multiple Array MatriX MAX Devices

PIA Programmable Interconnect Array

22

Programmable Logic Devices

Logic Array Block

23

Programmable Logic Devices

FLEX Devices

24

Programmable Logic Array - PLA

y1

y2

25

Programmable Array Logic - PAL

y1

y2