C.A.D. Agenda - PowerPoint PPT Presentation

Title:

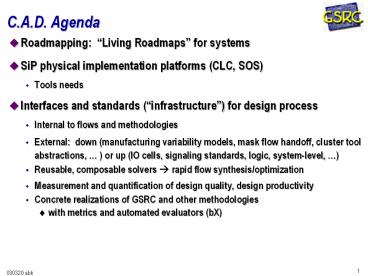

C.A.D. Agenda

Description:

Reusable, composable solvers rapid flow synthesis/optimization ... isomorphism, Odawara/Szymanski/Nijssen-Jess/Varadarajan-Arikati on regularity extraction ... – PowerPoint PPT presentation

Number of Views:20

Avg rating:3.0/5.0

Title: C.A.D. Agenda

1

C.A.D. Agenda

- Roadmapping Living Roadmaps for systems

- SiP physical implementation platforms (CLC, SOS)

- Tools needs

- Interfaces and standards (infrastructure) for

design process - Internal to flows and methodologies

- External down (manufacturing variability

models, mask flow handoff, cluster tool

abstractions, ) or up (IO cells, signaling

standards, logic, system-level, ) - Reusable, composable solvers ? rapid flow

synthesis/optimization - Measurement and quantification of design quality,

design productivity - Concrete realizations of GSRC and other

methodologies - with metrics and automated evaluators (bX)

2

Infrastructure and Benchmarking Agenda

- Today 900 1000

- BX and Benchmarking Status

- Saurabh Adya new Placement Utilities slot

- Aaron Ng Creating a Living Benchmarking

Resource Using BX - Today 1000 1100

- Placement-Centered Directions (Mini-Flows, New

Problems) - Xiaojian Yang Industry suggestions

- Today 1100 1230 pm

- Concrete steps with OpenAccess

- Mark Bales OA status update

- Discussion

3

Placement-Centered Open Problems

- Incremental Placement

- Combined Placement and Floorplanning

- ltClustering cells Floorplanning clustersblocks

Placing cellsgt locks solution into a bad subspace - Timing is a constraint (not an objective) WL is

an objective - Problem lack of understanding of

interrelationships between different objectives,

e.g., timing, area (fixed-die) and congestion - N.B. WL may not really be an objective it is a

proxy for congestion (area) - Issue of capturing timing in top-down

partitioning-based placement (partitioning is

net-based timing is path-based) - Open question How is SI solved at placement?

- IR drop placement?

- Variability-aware placement?

4

Placement-Centered Open Problems

- Thermal placement (not just dynamic power

minimization) - Given activities of all gates, find a placement

to minimize a linear combination of dynamic power

and maximum thermal variation - Hierarchy-driven placement?

- Probably moving to flat, so this seems less

important - Datapath-based (timing-constrained) placement

- People have tried but have not achieved notably

better results - 2 literature from late 1980s Ebeling et al.

subgraph isomorphism, Odawara/Szymanski/Nijssen-Je

ss/Varadarajan-Arikati on regularity extraction

5

Placement-Centered Open Problems

- Power implications (voltage islands)

- Chuck also mentions this

- Clock gating

- Multi-Vdd islands granularity of several

hundred cells (?) 1-2 rows min in V, stripe

pitch min in H - Ground islands (shutdown of blocks keeping memory

partially powered up) - Cf. Amirs work at Northwestern 1995

- Placement for BIST (check with Tim Cheng et al.)

- Signal Integrity Issues (crosstalk handling at

floorplan and placement) - Clock distribution

- ABK Suggestion Single-width, single-pitch cell

layout, synthesis, place and route flow WOULD BE

HEROES !!! (PhasePhirst!, SCAAM, etc.

next-generation lithography proposals, all of

which depend on hyper-resolution (2-beam

imaging) ? basically, only one direction and one

pitch will print (the layout is a subset of a

grating). Goal C.A.D. people should prove a

one-time, bounded hit on Moores Law (e.g., 30

density) but then scalability of SPR thereafter.

6

Placement-Centered Open Problems

- X, Y Architectures March 5th EE Design ?

- Design for Variability

- Backend Process Optimization

- Complex objective marketing, methodology,

integration - Marketing BEOL should be optimized for many

designs (derivatives, etc.) range of size,

frequency, etc. - Methodology Crosstalk, IR drop, routing

density, etc. - Statistical information WL per layer,

designs having X gates, Y MHz, - Integration cost of fabrication (e.g., AR

limits, low metal-layer count, layers, thickness

(mfg throughput, pitch LBs from AR limits, ))

![get⚡[PDF]❤ Pocket Planner 2024-2025: Small 2-Year Monthly Agenda for Purse | 24 Months PowerPoint PPT Presentation](https://s3.amazonaws.com/images.powershow.com/10081698.th0.jpg?_=20240719098)

![[PDF] DOWNLOAD Agenda 2021: Poker, crâne | Janvier à Décembre 2021 | A PowerPoint PPT Presentation](https://s3.amazonaws.com/images.powershow.com/10095955.th0.jpg?_=20240811046)