Multiplexers - PowerPoint PPT Presentation

1 / 17

Title:

Multiplexers

Description:

Encoders. Encoders are the ... For an 8-3 encoder, there should be 256 rows in ... Priority Encoder: If more than one input is 1', more significant bit ... – PowerPoint PPT presentation

Number of Views:161

Avg rating:3.0/5.0

Title: Multiplexers

1

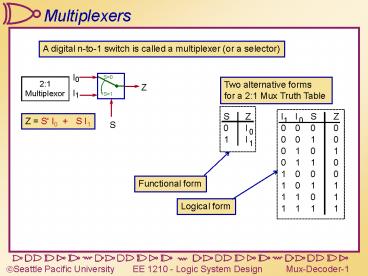

Multiplexers

A digital n-to-1 switch is called a multiplexer

(or a selector)

Two alternative forms for a 21 Mux Truth Table

Functional form

Logical form

2

Multiplexers

3

VHDL Muxes

LIBRARY ieeeUSE ieee.std_logic_1164.allENTITY

mux4to1 IS PORT( data IN STD_LOGIC_VECTOR(3

downto 0) sel IN STD_LOGIC_VECTOR(1

downto 0) z OUT STD_LOGIC)END mux4to1

Remember the IEEE library!

Inputs data3..0,sel1..0Output Z

ARCHITECTURE behavior OF mux4to1

ISBEGINPROCESS(data,sel)BEGIN CASE sel

IS WHEN "00" gt z lt data(0) WHEN "01" gt z

lt data(1) WHEN "10" gt z lt data(2) WHEN

"11" gt z lt data(3) WHEN others gt z lt 0

END CASEEND PROCESSEND behavior

If Data or Sel change, output (Z) can change

Set up as a CASE statement

WHEN OTHERS Use this even if there arent any

others

4

Cascading Muxes

Large multiplexers can be implemented by cascaded

smaller muxes

Control signals S1 and S0 simultaneously choose

one of I0-I3 and I4-I7 Control signal S2 chooses

which of the upper or lower MUX's output to gate

to Z

Alternative 81 Mux Implementation

5

Using Muxes as logic blocks

2n-11 multiplexer can implement any function of

n variables n-1 control variables remaining

variable is a data input to the mux

F(C,B,A) m0 m2 m6 m7

1

Lookup Table

0

0

1

6

Optimized LUTs

F(C,B,A) m3 m4 m6 m7

0

0

CB00 F0

F

A

A

CB01 FA

1

CB10 FA

C

B

1

CB11 F1

We can fit a function of n variables into a

2n-11 mux by using this trick (note may require

one inverter)

7

Using a multiplexor as a switch

Consider a computer system with CPU, memory, I/O

devices, etc. Each one needs to be able to

communicate with the others

- Pros

- Conceptually simple

Memory

- Cons

- Lots of wires

- Each device needs separate output and input

ports - 32-bit mux is a large device

CPU

41 x 32bit Mux

Disk

00

Control

Example Read a value from memory into CPU

Keyboard

8

Using a Bus

Bus Bidirectional, Driven by one device at a

time

Memory

A few (2-3) control lines to each device

- Pros

- Much fewer wires

- Simpler wiring

- Expandable

- One data port per device

CPU

Control

Disk

- Cons

- More complex electrically

- Must manage bus

Keyboard

Critical issue Were connecting multiple outputs

together. Bad Idea!

Example Read a value from memory into CPU

9

Smoke Happens

OK to connect one output to multiple inputs

1

0

Not OK to connect outputs together!

Direct connection from power to ground smoke!

10

Tri-State Inverter

En1

Enable

High-Impedance (Hi-Z) state

En0

En Out

0 Z

1 In

Modify an inverter

Tri-state Inverter

11

Using tri-state gates

Goal Connect three selectable inputs to a common

output

Whenever a select signal is asserted,that input

is connected to the output

Must make sure that there is always exactly one

driver turned on!

12

Demultiplexers

Demultiplexer One data input, n control inputs,

2n outputs

Control inputs (called selects) - Binary index of

output to which the input is connected

Data input usually called enable (G or E)

12 Demultiplexer

13

Larger Demultiplexers/Decoders

18 Demultiplexer

38 Decoder

14 Demultiplexer

24 Decoder

If we view the G signal as an enable, then a

demultiplexer simply decodes the binary select

signal into a unary output signal ? Decoder

- Decoder

- Enable0? all outputs are 0

- Enable1? output is unary representation of

binary select input

14

Decoders In VHDL

LIBRARY ieeeUSE ieee.std_logic_1164.allENTITY

Decoder2to4 IS PORT( s IN STD_LOGIC_VECTOR(1

downto 0) en IN STD_LOGIC y

OUT STD_LOGIC_VECTOR(3 downto 0)) END

Decoder2to4

ARCHITECTURE logicfunc OF Decoder2to4

IS BEGIN PROCESS(s,en) BEGIN IF (en1)

THEN CASE (s) IS WHEN 00 gt y lt

0001 WHEN 01 gt y lt 0010 WHEN

10 gt y lt 0100 WHEN 11 gt y lt

1000 WHEN OTHERS gt y lt 0000 END

CASE ELSE y lt 0000 END IF END

PROCESS END logicfunc

Sensitive to changes in s or en

Only consider when en 1

Go through cases for all possible inputs

If en 0, then output 0000

15

Encoders

Encoders are the opposite of decoders

Binary output y2..0 Corresponds to the index

of the input that is 1

Unary input w7..0 exactly one of the eight

inputs is 1

For an 8-3 encoder, there should be 256 rows in

the truth table

Only rows with exactly one 1 are valid ? Eight

valid rows

16

Priority Encoders

What if more than one input to and encoder is

1? ? Invalid input ? Output is undefined

Priority Encoder If more than one input is 1,

more significant bit has priority Add a z

output ? true when no inputs are 1

17

VHDL Priority Encoder

LIBRARY ieeeUSE ieee.std_logic_1164.allENTITY

Priority8 IS PORT( w IN STD_LOGIC_VECTOR(7

downto 0) y OUT STD_LOGIC_VECTOR(2

downto 0) z OUT STD_LOGIC)END Priority8

Remember the IEEE library!

Input w7..0Outputs y2..0, Z

ARCHITECTURE behavior OF Priority8

ISBEGINPROCESS(w)BEGIN IF (w(7)1) THEN

y lt 111 z lt 0 ELSIF (w(6)1) THEN y lt

110 z lt 0 ELSIF (w(5)1) THEN y lt

101 z lt 0 ELSIF (w(4)1) THEN y lt

100 z lt 0 ELSIF (w(3)1) THEN y lt

011 z lt 0 ELSIF (w(2)1) THEN y lt

010 z lt 0 ELSIF (w(1)1) THEN y lt

001 z lt 0 ELSIF (w(0)1) THEN y lt

000 z lt 0 ELSE y lt

000 z lt 1 END IFEND PROCESS END

behavior

Case statement would require 256 rows

Use cascaded IFs