Introduction to Multiplexers - PowerPoint PPT Presentation

1 / 15

Title:

Introduction to Multiplexers

Description:

Introduction to Multiplexers. Lecture Notes Lab 3 - Select one out of several bits ... For example, we can use Boolean algebra to simplify a three-input XOR to the ... – PowerPoint PPT presentation

Number of Views:141

Avg rating:3.0/5.0

Title: Introduction to Multiplexers

1

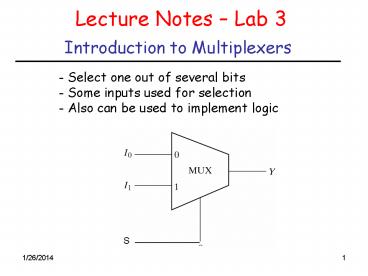

Introduction to Multiplexers

Lecture Notes Lab 3

- Select one out of several bits - Some inputs

used for selection - Also can be used to

implement logic

S

2

Introduction to Multiplexers

Lecture Notes Lab 3

True Table

3

4-to-1 multiplexer

Lecture Notes Lab 3

4

4-to-1 multiplexer

Lecture Notes Lab 3

5

4-to-1 multiplexer VHDL Implementation

Lecture Notes Lab 3

Architecture

ARCHITECTURE multiplexor4x1 OF mux4x1 IS BEGIN

PROCESS(S, D0, D1, D2, D3) BEGIN CASE

S IS WHEN "00" gt Y lt D0 WHEN "01"

gt Y lt D1 WHEN "10 gt Y lt D2

WHEN OTHERS gt Y lt D3 END CASE

END PROCESS END multiplexor4x1

Entity

ENTITY mux4x1 IS PORT ( S IN

STD_LOGIC_VECTOR (1 downto 0) D0 IN

STD_LOGIC D1 IN STD_LOGIC D2 IN

STD_LOGIC D3 IN STD_LOGIC Y OUT

STD_LOGIC ) END mux4x1

See details in the file mux4x1.vhd

6

Digital Arithmetic - Addition

Lecture Notes Lab 3

Block Diagram

A

S

B

1-bit adder

C

K

True Table

7

1-bit Adder Using Two 4-to1 Mux

Lecture Notes Lab 3

K-map for S

A A A A

0 A A 1

S

S

C

K-map for C

B K

B K

See VHDL implementation in addition.vhd

8

1-bit Adder Using Two 4-to1 Mux - VHDL

Lecture Notes Lab 3

Architecture

ARCHITECTURE addition_arch OF addition IS SIGNAL

sig1 STD_LOGIC_VECTOR (1 DOWNTO 0) BEGIN

sig1(1) lt B sig1(0) lt K P1 PROCESS

(sig1, A) BEGIN CASE sig1 IS WHEN

"00" gt S lt A WHEN "01" gt S lt

NOT(A) WHEN "10 gt S lt NOT(A)

WHEN OTHERS gt S lt A END CASE END

PROCESS P2 PROCESS (sig1, A) BEGIN

CASE sig1 IS WHEN "00" gt C lt 0

WHEN "01" gt C lt A WHEN "10 gt C

lt A WHEN OTHERS gt C lt 1 END

CASE END PROCESS END multiplexor4x1

Entity

ENTITY addition IS PORT ( A IN

STD_LOGIC B IN STD_LOGIC K IN

STD_LOGIC S OUT STD_LOGIC C OUT

STD_LOGIC ) END addition

9

Digital Arithmetic - Subtraction

Lecture Notes Lab 3

Block Diagram

X

D

1-bit subtraction

Y

B

b

True Table

10

1-bit Subtraction Using Two 4-to1 Mux

Lecture Notes Lab 3

Design a binary Subtractor Using Two 4to-1

Mux 1- K-map for D 2- Derive the inputs of the

mux D 3- K-map for B 4- Derive the inputs of the

mux B 5- Implement

11

Lecture 8 - XOR Gate

Operation

XOR (eXclusive OR)

Expressions

x ? y xy xy

Truth table

Logic gate

12

Lecture 8 - XOR Gate

- A two-input XOR gate outputs true when exactly

one of its inputs is true - XOR corresponds more closely to typical English

usage of or, as in eat your vegetables or you

wont get any pudding. - Several properties of the XOR operation

x ? y x y x y

13

More XOR

- The general XOR function is true when an odd

number of its arguments are true. - For example, we can use Boolean algebra to

simplify a three-input XOR to the following

expression and truth table.

x ? (y ? z) x ? (yz yz)

Definition of XOR x(yz yz) x(yz

yz) Definition of XOR xyz

xyz x(yz yz) Distributive

xyz xyz x((yz) (yz))

DeMorgans xyz xyz x((y z)(y

z)) DeMorgans xyz xyz x(yz

yz) Distributive xyz xyz

xyz xyz Distributive

K-map looks like that

yz

x

14

Adders using XOR

- A circuit called a full adder takes the carry-in

value into account

A ? (B ? Carry-in)

15

Parity generation using XOR

- For a given number of bits, attach a new bit 0 or

1, in order to ensure that the total number of 1s

is even (odd) - Remember the property of XOR it is true when an

odd number of its arguments are true.

Receiver detects the error (he computes the XOR

of 1111010, which gives 1.

Sender wants to transmit 110101 using even

parity. Then, it attach 0 (by computing the XOR

of 110101), i.e., 1101010

Channel

B

A

Channel flips a bit 1111010