SLC-Aware IOC LCLS Collaboration Jan 26, 2005 - PowerPoint PPT Presentation

1 / 15

Title:

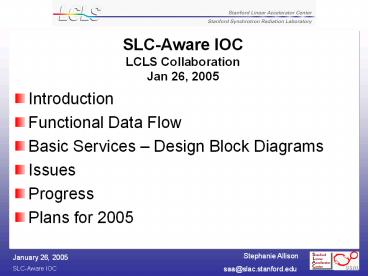

SLC-Aware IOC LCLS Collaboration Jan 26, 2005

Description:

Basic Services Design Block Diagrams. Issues. Progress. Plans for 2005 ... emulator. Fast Feedback over Ethernet. CA Gateway. Stephanie Allison. SLC-Aware IOC ... – PowerPoint PPT presentation

Number of Views:21

Avg rating:3.0/5.0

Title: SLC-Aware IOC LCLS Collaboration Jan 26, 2005

1

SLC-Aware IOC LCLS CollaborationJan 26, 2005

- Introduction

- Functional Data Flow

- Basic Services Design Block Diagrams

- Issues

- Progress

- Plans for 2005

2

Integration with the SLC Control System

EPICS W/S Distributed Applications

SLC Alpha All High Level Apps

Xterm

Xterm

EPICS W/S Distributed Applications

Xterm

Xterm

EPICS W/S Distributed Applications

EPICS W/S Distributed Applications

EPICS WS Distributed High Level Applications

CAS

CA Gateway

SLC Net over Ethernet (Data Transfer)

PNet (Pulse ID / User ID)

CA over Ethernet (EPICS Protocol)

MPG

I/OC (SLC-aware)

EVG

Micro emulator

P N E T

I/OC (SLC-aware)

Micro emulator

micro

CAMAC I/O

Fast Feedback over Ethernet

RF reference clock

3

Introduction SLC-Aware IOC

Provides data to SLC Apps from EPICS on demand

and periodically Performs requests by SLC Apps by

updating EPICS Messages over Ethernet no greater

than 10 Hz Requires significant development in

the IOC to emulate SLC micro in the IOC Used by

non-LCLS projects too

SLC Alpha Apps

Xterm

Xterm

Xterm

Xterm

SLC-Net over Ethernet

Vacuum Ctrl

E VG

LLRF

EVR

Diag

EVR

EVR

Pwr Supply Ctrl

C P U

C P U

C P U

HPRF I/O Boards

C P U

IOC

IOC

IOC

4

SLC IOC What it Will Do

- Receive SLC messages and act on them in the same

way as existing SLC micros for the following

functions - BPM-Like Data Acquisition (Gated ADCs) beam

synchronous - Magnet-Like Control and Readback (All Controlled

Devices) - PNET Timing Diagnostics

- Maintain its part of the VMS SLC database

- Receive the entire SLC database at initialization

time - Receive new setpoints at any time from the Alpha

- Send readbacks back to the Alpha on request and

periodically - Send setpoint changes made by external EPICS

applications to the Alpha - Goal same amount of network traffic as SLC

micros

5

SLC IOC What it Wont Do

- MPS

- BITBUS Power Supply Control

- KISNET Communication

- Micro-to-Micro Communication via Alpha

- SLC-style Analog Signal Monitoring

- SLC-style Digital Input/Output

- SLC-style Error Logging (use CMLOG instead)

- SLC-style Klystron Interface

- SLC-style Video Interface

- SLC-style Timing Interface (except PNET

diagnostics) - Direct Hardware Access (and no support for

virtual CAMAC commands) - Debugging from VMS

- SLC-Style Fast Feedback Interface

- Keep static data in the EPICS and SLC database

up-to-date

6

(No Transcript)

7

SLC Executive Design Block Diagram by Diane

Fairley

8

Message Service Design Block Diagram by Diane

Fairley

9

Database Service Design Block Diagram by Debbie

Rogind

10

IOC CMLOG Design Block Diagram by James Silva

11

SLC IOC Issues So Far

- Endian VMS to/from any possible EPICS platform

(64 bit processors NOT supported) - Memory LCLS CPUs that support SLC-aware IOC

should plan on gt256MB - Restart SLC tasks without restarting the IOC

- Detail diagnostics needed via the IOC shell, a

subset via CA - Keeping the EPICS and SLC database in-sync 2

master problem - Max number of micros in the SLC control system

may need to be increased - Possible need for a second proxy in the SLC

production control system - Outside the scope of the SLC-Aware IOC

- Changes to VMS SLC control system to support LCLS

high-level apps (i.e. modeling) - Changes to the VMS CA server to support any new

LCLS requirements - SLC database generation

- Tool to provide for consistent SLC and EPICS

databases

12

SLC-Aware IOC Progress

- Team in place

- LCLS Controls Stephanie Allison, Kristi Luchini,

Consultants - ESD Software Diane Farley, Debbie Rogind, Ron

MacKenzie, James Silva, Consultants - Weekly meetings, working web page and task list

in place - Basic Services

- Executive, Message, Database, CMLOG Services

Func reqts and design finished and reviewed with

only minor mods left to reflect as-built.

Implementation and test in final phase (2.5

full-time) - Async Utilities and Periodic Micro Health

Update Func reqts and design started (1

full-time) - Changes to VMS Programs done by ESD, new type

of micro added - Coding standards in place, adopted by all LCLS

controls - Development environment in place, shared setup

scripts - Application Services

- Device Control and Readback (Magnet) Func reqts

started (1 part-time) - PNET Timing Diagnostics Func reqts started (1

part-time) - Gated ADC Acquisition (BPM) no significant

progress - Changes to VMS Programs not yet defined

13

SLC IOC Plans for 2005

- Func Reqts Reviews

- Async Utilities and Periodic Health Update

Early Feb - Device Control and Readback Mid Feb?

- PNET Timing Diags Late Feb

- Gated ADC Acq - March

- Design Reviews

- Async Utilities and Periodic Health Update Mid

Feb - Device Control and Readback Late Feb

- PNET Timing Diags March

- Gated ADC Acq - April

- Implementation

- Basic services April

- Start RTEMS and Linux testing April or sooner

- Device Control and Readback May

- PNET Timing Diags May

- Gated ADC Acq - June

- Fully operational prototype by Oct 2005

- Ready for first beam in LINAC by May 2007

14

Reference Slides Follow

15

Timing

Nsec resolution on the timing gates produced from

the Event Receiver 50 psec jitter pulse to

pulse PNET module gets beam code data from Master

Pattern Generator Beam code data transferred to

Event Generator Event generator sends events to

receivers including 360 Hz, 120 Hz, 10 Hz and 1

Hz fiducials last beam pulse OK Machine

mode EPICS time stamp Event receivers produce to

the IOC interrupts on events data from the

event generator in registers 16 triggers with

configurable delay and width

476 MHz RF Reference

SLC micro

MPG

FIDO

119 MHz w/ 360 Hz fiducial

128 bit beam code _at_ 360 Hz

Vacuum Ctrl

EVR

Diag

EVR

Power Supply Ctrl

C P U

E VG

L L R F

EVR

P N E T

C P U

C P U

C P U

IOC

IOC

IOC

16 triggers

16 triggers

Drive Laser Off

Machine Protection

Beam Code EPICS Time EPICS Events