Busses and Addressing - PowerPoint PPT Presentation

1 / 29

Title:

Busses and Addressing

Description:

'Selects' the chip on the board as either the 'source' for a read or the target for a 'write' ... data from data bus and stores it into register selected by ... – PowerPoint PPT presentation

Number of Views:44

Avg rating:3.0/5.0

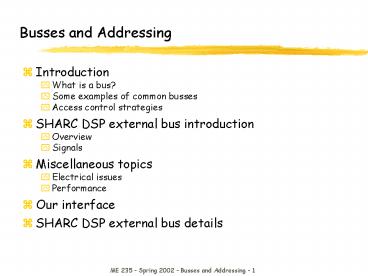

Title: Busses and Addressing

1

Busses and Addressing

- Introduction

- What is a bus?

- Some examples of common busses

- Access control strategies

- SHARC DSP external bus introduction

- Overview

- Signals

- Miscellaneous topics

- Electrical issues

- Performance

- Our interface

- SHARC DSP external bus details

2

What is a bus?

- Shared wire(s) that allow two or more devices to

be connected? - Two uses are common

- Bus internal to a computer

- Network

- Computers regularly have multiple busses

- Why is it called a bus?

- Origin was probably from electrical busbar

- Start thinking on the bus or off the bus.

3

Examples

- PCI bus in your PC (separate address and data)

- RS-485 serial bus (single data bit, S/W

addressing) - Ethernet

- SHARC external bus

4

Wide range of busses

- Many engineering tradeoffs

- Speed

- Cost

- Convenience of access

- Availability of wires

- Many design constraints results in many

optimization points.

5

Wide range of types

- Internal vs. external

- Internal typically wider

- Internal typically higher speed

- Internal typically higher performance

- Widths

- Modern designs often have multiple internal

busses, with different widths - Variety of access control

- More than one way to keep devices off the bus.

6

Wide range of speed

- Low speed

- Echelon networking over power wiring

- 100s of bits per second

- High speed

- VME

- PCI

- Speed typically measured in bits or bytes per

second - 32 bits wide, 66 MHz -gt 250 Mbytes/sec

- Much more on speed later - electrical speed is

not the only issue

7

Access control

- Important to keep multiple device from

transmitting at the same time - Many possible strategies, but all must limit

access to shared resources - Software and hardware both may be used to control

access - Examples

- Token passing, multi-master

- Master/slave

- Collision detect

8

Violation of access control

- Result is system dependent

- Ethernet handles gracefully - this condition is

designed in. - PCI - can be handled gracefully

- SHARC external bus - will possibly crash the

system. Will certainly not be handled gracefully.

9

Token passing access control

- Whoever has the token owns the shared resource

- Token may be passed between any two nodes

- Software token passing example

- RS-485

- Electrical description

- Software addressing

- Very low performance, but very cheap!

- Hardware token passing example

- Token Ring

- Electrical description

- High performance, deterministic

10

Collision detect access control

- When the bus is detected as idle, any node may

attempt to sieze it - When you want the bus and no one competes for it,

you get it - Collisions occur when two notes attempt to sieze

simultaneously - Ethernet as an example

- Addressing scheme

- Hubs

- Switches

- Performance (can be either high or low).

11

Master/slave example

- SHARC DSP external bus

- Single node masters the bus, granting access to

slaves according to some scheme (time slice,

prioritized, software flow, etc.) - Access may be either synchronous or asynchronous.

12

Synchronous bus

- Generally higher performance

- Devices on the bus must respond within a certain

amount of time - Clock is used to synchronize the devices on the

bus clock is used to validate each signal - Once clock speed is set, it is fixed for the life

of the bus (or at least the backward compatible

life of the bus).

13

Asynchronous bus

- A clock IS NOT used to synchronize slave devices

with the master - Slave devices must drive an acknowledge signal to

alert another node that the data on the wires is

stable - Higher speed devices may be added to the bus as

technology progresses without violating backward

compatibility.

14

Picture of our system

- Signals involved

- Address lines

- Data lines

- Chip select

- Write

- Read

- Acknowledge

- Interrupt

15

Address bus

- 24 bits, ADDR(230), 0 contains LSB of address

- Addressing overview

- LSB specifies one byte

- Examples

- Start thinking hex because of direct translation

to driven wires - Driven from SHARC side only

16

Data bus

- Can be driven from any node

- How can this work - think of a typical CMOS

buffer configuration - Tri-state output

- Must use output with enable for driving these

lines.

17

Tri-state output buffer

18

Chip select

- Perhaps most confusing signal

- Selects the chip on the board as either the

source for a read or the target for a write - Older systems generated CS from ADDR using

external logic (e.g. PAL) - More modern systems have CS generated in CPU

fixed to an address range - Current devices often have programmable CS

address range.

19

Read

- Asserted when master wants to read data from

slave - Results in OE from selected driver being driven

active - ACK must be driven back in an asynchronous bus to

signal that data is stable on the data wires - Data is multiplexed onto wires from the slave - 8

bits of data correspond to 8 pins on the FPGA

have 8 internal tri-state buffers, even though we

will have many logical registers.

20

Write

- Asserted when master wants to write data to a

slave - Dont need demultiplexers off of the bus -

connect the data bus to all registers, then

generate a load signal with an address - To how many registers can the output fan out? Is

buffering needed?

21

Acknowledge

- Must be driven low immediately after RD or WR is

driven active in order to hold the DSP - Will be driven back high to let the DSP know I

have gotten the data off of the data bus (in the

case of a read) or the data you want is on the

data bus (in the case of a write - When the DSP drives RD or WR inactive, the Xilinx

part must tri-state the ACK output.

22

Issues

- Fanout

- Speed

- Signal stability over long wires.

23

Performance

- System we are designing is relatively low

performance - Some thoughts about performance

- Build system all on one PCB to keep wire delays

short - Multi-master can allow higher performance

- Device prepares data and pushes it across bus

before interrupt is generated.

24

System level design

- 4 kHz clock drives cycle

- Xilinx copies transient data into stable

registers - Xilinx triggers INTR to SHARC, signalling that

new data is available - Processor reads input registers

- Processor can perform calculations

- Processor writes output registers

- Everything must happen in less than 200

microseconds check this with the scope.

25

Software side

- Processor nominal word size is 32 bit wide

- We are only providing 8 bits of data

- Our registers will be located 32 bits apart

(0x04) - Only 8 bits of the 32 bit read will contain valid

data.

26

Read register 3

- Code

- unsigned int r3raw

- unsigned char r3

- r3raw (unsigned int )0x2000000b

- r3 r3raw 0xff

- What happens?

- CS and address are driven onto address bus

- RD is driven

- FPGA sees RD, drives ACK low

- FPGA selects register, drives data bus using ADDR

controlled mux and OE for data bus controlled by

RD CS - When data is stable, FPGA drives ACK high

- When RD goes away, ACK and OE must go hi-Z

quickly.

27

Write register 1

- Code

- unsigned int r1raw

- r1raw (unsigned int )0x20000004

- r1raw 0xab

- What happens?

- CS and address are driven onto address bus

- WR is driven

- FPGA sees WR, drives ACK low

- FPGA takes data from data bus and stores it into

register selected by ADDR lines - When data has been stored to register, FPGA

drives ACK high - When WR goes away, ACK and OE must go hi-Z

quickly.

28

Details

- SHARC 21065L data sheet

- Page 16 for read

- Page 17 for write

29

Summary

- Addresses

- Have to start thinking in hex

- Addressing on FPGA and DSP sides are different

- Busses

- Make sure the wiring is correct

- Dont let FPGA and DSP handle registers at the

same time.