Exceptions PowerPoint PPT Presentation

1 / 14

Title: Exceptions

1

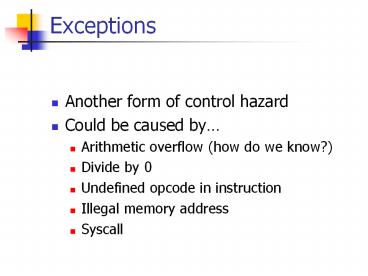

Exceptions

- Another form of control hazard

- Could be caused by

- Arithmetic overflow (how do we know?)

- Divide by 0

- Undefined opcode in instruction

- Illegal memory address

- Syscall

2

Handling an exception

- What the system must do

- Save address of offending instruction

- Transfer control to OS at some address that will

handle the exception - OS takes appropriate action

- OS can terminate execution, or continue using the

address saved in 1. - How this is done depends on processor

implementation (datapath, etc.)

3

MIPS support for exceptions

- EPC exception program counter

- contains address of instruction that caused the

exception - Cause 32-bit register used to record cause of

exception. - mfc0 instruction to put EPC into one of

general-purpose regs. E.g. mfc0 s1, epc - so that we can return from exception handler

using jr.

4

Exceptions in pipelined datapath

- Could have exceptions in different stages

- IF fetching instruction from memory causes page

fault - ID illegal opcode

- EX division by 0, overflow

- MEM fetching data causes page fault illegal

address (protection violation) - WB no exceptions possible!

5

Exceptions in pipelined datapath

- Say you execute

- lw 1, 4(3)

- add 2, 3, 4 causes overflow!!!

- or 3, 1, 2

- bne 1, 3, L

6

Exception in stage EX

ID

EX

MEM

WB

IF

EPC

Cause

bne 1, 3, L

Instruction memory

Register file

ALU

CLK

SE

PC

Data Memory

0x1240

Overflow detected add 2, 3, 4

or 3, 1, 2

lw 1, 4(3)

We need to continue executing lw, but kill the

add, or, and bne instructions and start

executing the exception handler instead

Clock

1

2

3

4

7

Exception in EX next cycle

ID

EX

MEM

WB

IF

EPC

Cause

exc. instr 1

Instruction memory

Register file

ALU

CLK

SE

PC

Data Memory

address of Interrupt handling routine

nop

nop

nop

lw 1, 4(3)

Clock

Still in pipeline!

1

2

3

4

5

8

Review and summary 1

- Performance

- CPI cycles per instruction.

- Average CPI based on instruction mixes

- Execution time IC CPI C

- Where IC instruction count C clock cycle

time - Performance inverse of execution time

- MIPS million instructions per second

- Higher is better

- Amdahls Law

9

Review and summary 2

- Differences between single-cycle, multi-cycle,

and pipelined datapaths. - CPI for single-cycle is 1. Inefficient.

- Multicycle instructions take different of

cycles to execute. CPI is 3,4, or 5 depending on

instruction type. - Pipeline fixed CPI 5 , but best throughput and

performance. - Multicycle share resources across cycles (e.g.

have one ALU for everything) not so in single

cycle and pipeline (e.g. have at least 3 ALUs).

10

Functional units

- Many units used the same in all datapaths

(single, multi, pipeline) - - has address of current instr.

- Sign-extend for I-type instructions (e.g.

addi), takes a 16-bit immediate field from

instruction and sign-extends it to 32 bits. - Shift-left-by-2 - used for adjusting

addresses to be word-aligned. - Branch address calculation (sign_ext(imm)) ltlt

2) (PC4)

PC

SE

ltlt 2

11

Controls

- Basic controls for some functional units

- Register file

- Write enable only 1 when writing a register

- Memory

- MemRead want to read data

- MemWrite want to write data (must be off by

default!) - ALU

- Operation to be performed

- PC

- PCWrite set to 1 when want to write PC. Only

exists in multicycle datapath. We write PC on

every cycle in pipelined/single cycle versions!

12

Controls continued

- Decisions to be made in the datapath (i.e. mux

controls) - ALUSrcA, ALUSrcB choose ALU inputs from

- register (read from register file)

- Immediate (sign-extended, zero-extended, etc.)

- Forwarded data (in pipelined design)

- PCSource select between PC4, branch address,

and jump address - RegDst select between rd and rt for destination

register - MemtoReg in pipeline, select between memory

output and ALU output to write back to register

file. - IorD in multicycle, select whether we use memory

to read instruction or data.

13

Pipelining

Clock Cycle 1

Clock Cycle 2

Clock Cycle 3

Clock Cycle 4

Clock Cycle 5

Clock Cycle 6

Clock Cycle 7

Time

IM

Reg

DM

instr1

IM

Reg

DM

instr2

IM

Reg

DM

instr3

IM

Reg

DM

instr4

Instructions

14

Pipeline hazards

- Data hazards

- Instruction dependent on another instruction

still in pipeline. - E.g. add 1, 2 3 or 3, 1, 1

- Resolve by forwarding and/or stalling

- Structural hazards

- where two instructions at different stages want

to use the same resource. - Resolve by adding more hardware

- Control hazards

- Branches, interrupts, exceptions

- Wrong instruction in pipeline following branch,

because branch address/condition not ready in

time - Fixes stall, redesign pipeline, specify delay

slots, branch prediction