Digital Processing Platform - PowerPoint PPT Presentation

Title:

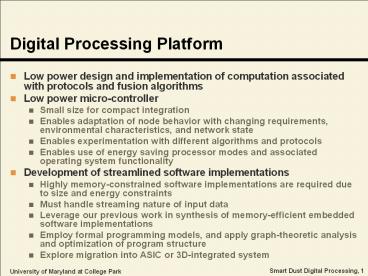

Digital Processing Platform

Description:

Digital Processing Platform Low power design and implementation of computation associated with protocols and fusion algorithms Low power micro-controller – PowerPoint PPT presentation

Number of Views:62

Avg rating:3.0/5.0

Title: Digital Processing Platform

1

Digital Processing Platform

- Low power design and implementation of

computation associated with protocols and fusion

algorithms - Low power micro-controller

- Small size for compact integration

- Enables adaptation of node behavior with changing

requirements, environmental characteristics, and

network state - Enables experimentation with different algorithms

and protocols - Enables use of energy saving processor modes and

associated operating system functionality - Development of streamlined software

implementations - Highly memory-constrained software

implementations are required due to size and

energy constraints - Must handle streaming nature of input data

- Leverage our previous work in synthesis of

memory-efficient embedded software

implementations - Employ formal programming models, and apply

graph-theoretic analysis and optimization of

program structure - Explore migration into ASIC or 3D-integrated

system

2

Example of Software Structure

Receiver

No new data

Periodic wake-up

Sensor

Transmitter

No

Broadcast new data

Extract data

Need to update neighbors?

Yes

3

Protocol Set-up and System Configuration

- Handshaking

- Source channel coding

- Integrate with transceiver to establish PLL

timing - Establish error correction coding

- Establish low-complexity decoding

- Assign transmission power

- Assign processing tasks to network nodes

4

System-level Optimization ExampleTask

Assignment Algorithms

- Need to balance communication and computation

throughout the network - Develop models of power consumption in network

nodes and communication links - Develop task graph models of overall network

functionality - Develop algorithms to embed task graph algorithm

specifications into the network - Assign processing tasks to network nodes

- Turn off idle nodes

- Large design space

- Explore evolutionary algorithms to optimize task

graph embeddings

5

Evolutionary Algorithms

Decoding function

Genetic operators

Genotype space(Genetic representation)

G(t)

6

Digital Design Summary

- Contributions

- Low power, memory-constrained implementation

techniques - Application-specific optimization of software and

VLSI - Integrated optimization of protocols and system

configuration - Selected Prior Work

- N. K. Bambha, S. S. Bhattacharyya, J. Teich, and

E. Zitzler. Systematic integration of

parameterized local search in evolutionary

algorithms. IEEE Transactions on Evolutionary

Computation. To appear. - S. S. Bhattacharyya. Hardware/software

co-synthesis of DSP systems. In Y. H. Hu, editor,

Programmable Digital Signal Processors

Architecture, Programming, and Applications,

pages 333-378. Marcel Dekker, Inc., 2002. - P. K. Murthy and S. S. Bhattacharyya. Shared

buffer implementations of signal processing

systems using lifetime analysis techniques. IEEE

Transactions on Computer-Aided Design of

Integrated Circuits and Systems, 20(2)177-198,

February 2001. - S. S. Bhattacharyya, R. Leupers, and P. Marwedel.

Software synthesis and code generation for DSP.

IEEE Transactions on Circuits and Systems --- II

Analog and Digital Signal Processing,

47(9)849-875, September 2000.

![How to Start a Digital Marketing Agency in India? [Step by Step Guide] PowerPoint PPT Presentation](https://s3.amazonaws.com/images.powershow.com/9441593.th0.jpg?_=202005190312)