Instruction Fetch - PowerPoint PPT Presentation

Title:

Instruction Fetch

Description:

Execution, Memory Address Computation, or Branch Completion ... It exploits parallelism among the instruction in a sequential instruction stream ... – PowerPoint PPT presentation

Number of Views:62

Avg rating:3.0/5.0

Title: Instruction Fetch

1

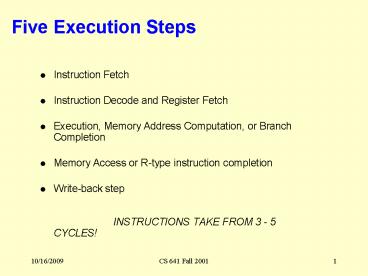

Five Execution Steps

- Instruction Fetch

- Instruction Decode and Register Fetch

- Execution, Memory Address Computation, or Branch

Completion - Memory Access or R-type instruction completion

- Write-back step INSTRUCTIONS TAKE FROM 3 - 5

CYCLES!

2

(No Transcript)

3

Step 1 Instruction Fetch

- Use PC to get instruction and put it in the

Instruction Register. - Increment the PC by 4 and put the result back in

the NPC. - Can be described succinctly using RTL

"Register-Transfer Language" IR

MemoryPC NPC PC 4What is the

advantage of updating the PC now?

4

Step 2 Instruction Decode and Register Fetch

- Read registers rs and rt in case we need them

- Compute the branch address in case the

instruction is a branch - RTL A RegIR25-21 B

RegIR20-16 aluout PC (sign-extend(IR15-

0)) - We aren't setting any control lines based on the

instruction type (we are busy "decoding" it in

our control logic)

5

Step 3 (instruction dependent)

- ALU is performing one of three functions, based

on instruction type - Memory Reference ALUOut A

sign-extend(IR15-0) - R-type ALUOut A op B

- Branch if (A op 0) PC ALUOut

6

Step 4 (R-type or memory-access)

- Loads and stores access memory MDR

MemoryALUOut or MemoryALUOut B - R-type instructions finish RegIR15-11

ALUOutThe write actually takes place at the

end of the cycle on the edge

7

Write-back step

- RegIR20-16 MDR

- What about all the other instructions?

8

Summary

9

Simple Questions

- How many cycles will it take to execute this

code? lw r2, 0(r3) lw r3, 4(r3) beqz r2,

Label assume not add r5, r2, r3 sw 8(r3),

r5Label ... - What is going on during the 8th cycle of

execution? - In what cycle does the actual addition of r2 and

r3 takes place?

10

Enhancing Performance

- Pipelining is an implementation technique in

which multiple instructions are overlapped in

execution - It improves instruction throughput rather than

individual instruction execution time - It exploits parallelism among the instruction in

a sequential instruction stream - Under ideal conditions the speedup from

pipelining equals the number of pipe stages - But there is some overhead associated with

pipelining so SU is not ideal - No stage may be faster than the slowest stage of

the pipe, or to put it another way, the slowest

instruction determines the total time for the pipe

11

Pipeline Example

- From HP, have seven single-cycle instructions

with various timings in a five-stage pipe - Sequential execution

12

Pipeline Example (Contd)

- Using a 2 nsec clock cycle with pipelining

- Recall that pipelining improves performance by

increasing instruction throughput as opposed to

decreasing the execution time of an individual

instruction - Notice the idle time in the pipe at certain times

13

Pipeline Performance

- Ideal speedup is number of stages in the

pipeline. Do we achieve this? - Throughput º task completed / unit time

- Given k tasks and an n-stage pipeline where each

stage takes the same unit of time to process and

task arrive at the same unit time intervals - It takes n time units to fill pipeline and

process first task - Thereafter, pipeline processes 1 task every unit

of time

Tp(k,n) n (k-1)

k

Throughput

n (k - 1)

14

Computer Pipelines

- Execute billions of instructions, so throughout

is what matters - DLX desirable features all instructions same

length, registers located in same place in

instruction format, memory operands only in loads

or stores

15

5 Steps of DLX DatapathFigure 3.1, Page 130

Memory Access

Write Back

Instruction Fetch

Instr. Decode Reg. Fetch

Execute Addr. Calc

IR

L M D

16

Pipelined DLX DatapathFigure 3.4, page 137

Instruction Fetch

Instr. Decode Reg. Fetch

Execute Addr. Calc.

Write Back

Memory Access

- Data stationary control

- local decode for each instruction phase /

pipeline stage

17

Graphically Representing Pipelines

?1998 Morgan Kaufmann Publishers

- Need to answer questions like

- How many cycles does it take to execute this

code? - What is the ALU doing during cycle 4?

- Use this representation to help understand

datapaths

ALU

ALU

18

Visualizing PipeliningFigure 3.3, Page 133

Time (clock cycles)

I n s t r. O r d e r