Real-Time Unit (RTU) - PowerPoint PPT Presentation

1 / 1

Title:

Real-Time Unit (RTU)

Description:

Arbiter. Arbiter. Static processor priority. Dynamic ... Provides the arbiter with processor priorities via priority bus. Arbitration Unit. Functionality ... – PowerPoint PPT presentation

Number of Views:25

Avg rating:3.0/5.0

Title: Real-Time Unit (RTU)

1

Static processor priority

Dynamic processor priority

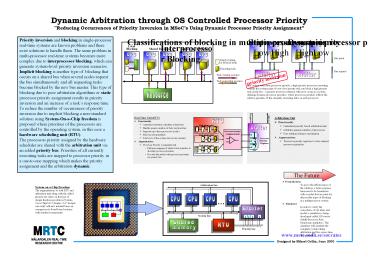

Classifications of blocking in multiprocessor

systems

Priority inversion and blocking in

single-processor real-time systems are known

problems and there exist solutions to handle

them. The same problem in multi-processor

real-time systems becomes more complex due to

interprocessor blocking, which can generate

system-level priority inversion scenarios.

Implicit blocking is another type of blocking

that occurs on a shared bus when several nodes

request the bus simultaneously and all

requesting tasks become blocked by the new bus

master. This type of blocking due to poor

arbitration algorithms or static processor

priority assignment results in priority inversion

and an increase of a tasks response time. To

reduce the number of occurrences of priority

inversion due to implicit blocking a non-standard

solution using System-On-a-Chip freedom is

proposed where priorities of the processors are

controlled by the operating system, in this case

a hardware scheduling unit (RTU).

The processors priority

assigned by the hardware scheduler are shared

with the arbitration unit via an added priority

bus. Priorities of all currently executing tasks

are mapped to processor priority in a one-to-one

mapping which makes the priority assignment and

the arbitration dynamic.

Interprocessor Blocking

CPU

CPU

CPU

CPU

Local

Low

High

Low

High

Blocking

Shared Resource

Implicit Bus-Blocking

H

L

H

L

CPU

CPU

CPU

CPU

CPU

Bus grant

Ready,waiting,

or blocked tasks

Executing task

Bus request

Arbiter

Arbiter

Task owning resource

priority inversion

Task requesting resource

In a system with static processor priority, a

high priority processor executing a (from the

system point of view) low priority task can block

a high priority task on the bus. A priority

inversion situation will never occur in a system

utilising dynamic processor priorities, where

processor priorities reflects the relative

priorities of the currently executing tasks on

each processor.

Resource

- Real-Time Unit (RTU)

- Functionality

- Centralised real-time scheduler in hardware

- Handles generic number of tasks and priorities

- Supports up to three processors (today)

- Microsecond granularity

- Total view of the system state (at any instant)

- Augmentations

- Processor Priority Assignment unit

- Performs mapping of relative task priorities to

absolute processor priorities - Provides the arbiter with processor priorities

via priority bus

- Arbitration Unit

- Functionality

- Centralised priority based arbitration unit

- Arbitrates generic number of processors

- Uses arbitrary fairness mechanism

- Augmentations

- Processor priority registers to store current

processor priorities

Requests

Grants

RTU

Task queue cpu1

Arbiter

0

7

1

3

Processor Priority

1

Assignment unit

Task queue cpu2

2

6

9

Processor Priority Registers

3

Task queue cpu3

2

1

4

5

6

The Future

- Formalisation

- To prove the effectiveness of the solution, a

tasks response time need to be formalised with a

model that accounts for all possible types of

blocking in a multiprocessor system. - Simulator

- In order to verify the correctness of our ideas

and model, a simulator is being developed called

MP-rmsim (Multi-Processor Rate Monotonic

simulator). The simulator will simulate the

complete system taking arbitration and bus access

time into account.

Arbitration bus

System-on-a-Chip Freedom The augmentations to

both RTU and arbitration unit along with the

added priority bus relies on the type of design

freedom possible in System-On-a-Chip(SoC)

designs. SoC designs can easily add new internal

buses in comparison to board based systems with

standard components.

...

CPU

CPU

CPU

CPU

Arbiter

System bus

Shared

RTU

memory

Priority bus

www.mrtc.mdh.se/socrates