Sequence Detectors - PowerPoint PPT Presentation

1 / 10

Title:

Sequence Detectors

Description:

Sequence detection is the act of recognizing a predefined series of inputs ... process1: PROCESS(CLK) VARIABLE STATE : STD_LOGIC_VECTOR(1 DOWNTO 0):= '00'; BEGIN ... – PowerPoint PPT presentation

Number of Views:261

Avg rating:3.0/5.0

Title: Sequence Detectors

1

Sequence Detectors

Lecture Notes Lab 5

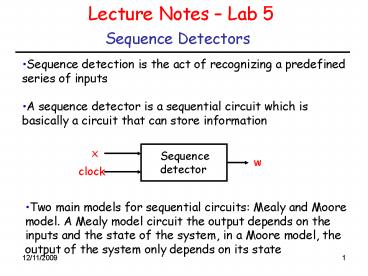

- Sequence detection is the act of recognizing a

predefined series of inputs - A sequence detector is a sequential circuit which

is basically a circuit that can store information

x

Sequence detector

w

clock

- Two main models for sequential circuits Mealy

and Moore model. A Mealy model circuit the output

depends on the inputs and the state of the

system, in a Moore model, the output of the

system only depends on its state

2

Sequential circuits - Sequence detectors

Lecture Notes Lab 5

Storage elements

A combinational circuit and storage elements are

interconnected to form a sequential circuit. The

information stored at any time defines the state

of the circuit at that time. The next state of

the storage elements is a function of the inputs

and the present state. Synchronous sequential

circuit can be defined from the knowledge of its

signals at discrete instants.

3

A sequence detector of 110

Lecture Notes Lab 5

x

Sequence detector

w

clock

Values are only important on the rising edges of

the clock pulses

4

Moore State Machine for the sequence detector 110

Lecture Notes Lab 5

1

1

0

1

0

A/0

B/0

C/0

D/1

0

1

0

A

B

C

D

state

A

5

VHDL implementation for a sequence detector 110

Lecture Notes Lab 5

ARCHITECTURE seq_det_arch of seq_det

is BEGIN process1 PROCESS(CLK) VARIABLE STATE

STD_LOGIC_VECTOR(1 DOWNTO 0) "00"

BEGIN IF (CLK 1) THEN CASE STATE

IS WHEN "00" gt --

State A IF (X '0') THEN

STATE "00" W lt '0'

ELSE STATE "01" W lt '0' END

IF WHEN "01" gt -- State B

IF (X '1') THEN STATE "10" W lt

'0' ELSE STATE "00" W lt

'0' END IF

ENTITY seq_det IS PORT ( CLK

IN STD_LOGIC X IN

STD_LOGIC W OUT STD_LOGIC

) END seq_det

Continued

6

Lecture Notes Lab 5

VHDL implementation for a sequence detector 110

WHEN "10" gt -- State C

IF (X '1') THEN STATE "10"

W lt '0' ELSE STATE

"11" W lt '1' END IF WHEN

OTHERS gt -- State D IF (X

'1') THEN STATE "01"

W lt '0' ELSE STATE "00"

W lt '0' END IF END

CASE END IF END PROCESS END

seq_det_arch

7

Lecture Notes Lab 5

VHDL implementation for a sequence detector 10010

8

Lecture Notes Lab 5

Waveform Sequence detector for 10010

9

Design a sequence detector

Lecture Notes Lab 5

- Specs- Synchronous with CLK- Serial input X-

The sequence to be detected is 00101- Output Z

00000 when no sequence is detected,

00001 when the first bit of the sequence

is detected, 00010 when the second bit

is detected, 00100 when the

third bit is detected, 01000

when the fourth bit is detected, and

10000 when the whole sequence is

detected- If input Y is one, the system is reset

to output 00000

10

Design a sequence detector

Lecture Notes Lab 5

- Step 1 Block diagram of the system- Step 2

Design the state machine for the system- Step

3 Implement the system in VHDL- Step 4

Simulate the system implemented in step 4- Step

5 Program the Xilinx chip and test the system