Review of exponential charging and discharging in RC Circuits - PowerPoint PPT Presentation

1 / 16

Title:

Review of exponential charging and discharging in RC Circuits

Description:

Title: Review of exponential charging and discharging in RC Circuits Author: William Oldham Last modified by: Sheila Ross Created Date: 8/3/1999 4:47:57 AM – PowerPoint PPT presentation

Number of Views:32

Avg rating:3.0/5.0

Title: Review of exponential charging and discharging in RC Circuits

1

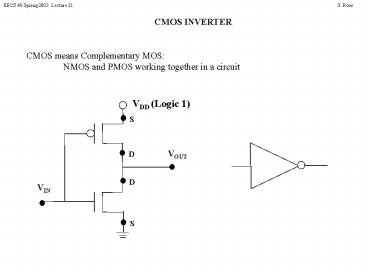

CMOS INVERTER

CMOS means Complementary MOS NMOS and PMOS

working together in a circuit

VDD (Logic 1)

S

VOUT

D

D

VIN

S

2

CMOS INVERTER RESPONSE

VOUT

VDD

VM Voltage when VIN VOUT ( VM)

VIN

D

C

B

E

A

VDD

3

LAST TIME SINGLE TRANSISTOR CIRCUIT

ID

triode mode

saturation mode

VGS 3 V

VDS VGS - VTH(N)

X

Linear ID vs VDS given by surrounding circuit

VGS 1 V

X

VDS

4

ANALYSIS OF INVERTER CIRCUT

- Obtain

- the two nonlinear ID vs. VDS equations for the

transistors ID(N) vs. VDS(N) and ID(P) vs.

VDS(P) - A linear relationship between ID(N) and ID(P)

(e.g., via KCL) - An independent linear relationship between VDS(N)

and VDS(P) (e.g. via KVL) - Using the above, write

- ID(P) vs. VDS(P) in terms of ID(N) vs. VDS(N) (or

vice-versa) - Solve the two transistor equations simultaneously.

5

ANALYSIS OF INVERTER CIRCUIT UNLOADED

VDD (Logic 1)

- Transistor equations

- ID(N) fN(VDS(N))

- ID(P) fP(VDS(P))

- ID(P)ID(N) 0

- VDS(N)-VDS(P) VDD

- Rewrite 1) as

- ID(N) -fP(VDS(N)-VDD)

S

VOUT

D

D

VIN

S

Find simultaneous solution to ID(N)

fN(VDS(N)) ID(N)

-fP(VDS(N)-VDD)

6

ANALYSIS OF INVERTER CIRCUIT UNLOADED

VDD (Logic 1)

Also note VGS(N) VIN VGS(P) VIN -

VDD VOUT VDS(N)

VGS(P) -

S

VOUT

D

VDS(N) _

D

VIN

VGS(N) -

S

7

CMOS INVERTER REGION A

ID

VGS(N) lt VTH(N)

VDS(P) VGS(P) - VTH(P)

VGS(P) lt VTH(N) - VDD

No current flow in Region A!

NMOS cutoff mode PMOS triode mode

VDS

VDD

8

CMOS INVERTER REGION B

ID

VGS(N) VTH(N) e

VDS(P) VGS(P) - VTH(P)

VGS(P) VTH(N) e - VDD

NMOS saturation mode PMOS triode mode

VDS(N) VGS(N) - VTH(N)

VDS

VDD

9

CMOS INVERTER REGION C

ID

NMOS saturation mode PMOS saturation mode

VDS(P) VGS(P) - VTH(P)

VDS(N) VGS(N) - VTH(N)

VDS

VDD

10

CMOS INVERTER REGION D

VGS(N) VDD VTH(P) - e

ID

VGS(P) VTH(P) - e

VDS(N) VGS(N) - VTH(N)

NMOS triode mode PMOS saturation mode

VDS(P) VGS(P) - VTH(P)

VDS

VDD

11

CMOS INVERTER REGION E

VGS(N) gt VTH(P) VDD

ID

VDS(N) VGS(N) - VTH(N)

VGS(P) gt VTH(P)

No current flow in Region E!

NMOS triode mode PMOS cutoff mode

VDS

VDD

12

CMOS INVERTER RESPONSE CURRENT FLOW

ID

VIN

D

C

B

E

A

VDD

13

- No ID current flow in Regions A and E if nothing

attached to output current flows only during

logic transition - If resistor or diode attached to output, current

will flow through PMOS when input is low (output

is high) - If another inverter (or other CMOS logic)

attached to output, transistor gate terminals of

attached stage do not permit current current

flows only during logic transition

VDD

S

VOUT2

D

D

VIN

S

14

EXAMPLE RESISTIVE LOAD

VDD 5 V

Find the power absorbed by the resistor and the

inverter. Power absorbed by inverter P

ID(P)VDS(P) ID(N)VDS(N)

S

VOUT

D

D

VIN 0 V

Let W/L m COX 1 mA, VTH(N) -VTH(P) 1 V, l

0.

1 kW

S

- Transistor equations

- ID(N) 0 A (NMOS cutoff)

15

EXAMPLE RESISTIVE LOAD

- ID(N) and ID(P) relationship

- ID(P)ID(N) -VOUT / 1 kW

- VDS(N) and VDS(P) relationship

- VDS(N)-VDS(P) VDD

VDD 5 V

S

VOUT

D

D

VIN 0 V

1 kW

S

4) Substitute into PMOS transistor equation

16

EXAMPLE RESISTIVE LOAD

- Solutions

- VDS(P) -8.87 V, -1.13 V

- VDS(P) -1.13 V agrees with triode mode

- ID(P) -3.24 mA

VDD 5 V

S

VOUT

D

D

VIN 0 V

1 kW

S

Power absorbed by inverter ID(P)VDS(P)

ID(N)VDS(N) 3.66 mW Power absorbed by

resistor R I2 (1 kW)(-3.24 mA)2 10.5 mW