1. VHDL? ?? ?? - PowerPoint PPT Presentation

1 / 85

Title: 1. VHDL? ?? ??

1

- 1. VHDL? ?? ??

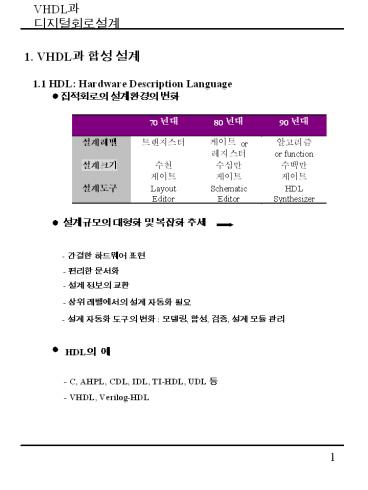

- 1.1 HDL Hardware Description Language

- ????? ????? ??

- ????? ??? ? ??? ??

- - ??? ???? ??

- - ??? ???

2

- 1.2 VHDL? ??? ??

- VHDL(VHSIC HDL)? ??

- - 1981? 6? ?? Woods Hole?? ??? ????

???? - Workshop?? ????? VHSIC(Very High

Speed Integrated - Circuit) ?????? ???? HDL??? ????

?? - ????? HDL ??(Department of

Defense Requirements for - HDL)??? ?? ??? ??

VHDL??? ?? - - 1983? 7? Intermetrics, IBM, Texas

Instruments ?? ??? - ?? ??? ??

- - 1985? VHDL 7.2 Version ??

???? ??? ??? - ???? ?????? ?

- - 1987? 12? IEEE 1076 ?? ??

?????? ?? ?? ?? - ??? ?????? ????? ??? ? ??? ??

3

- VHDL? ??? ??? ??

- - ?? ???? ??

- ?? ??????? ?? ?? ??

- ?? ??? ?? ?? ?? ? ??

??? ??? - ?? ??? ??

- - ??? ? ??

- ??? ????? ??? ??

??? ?? - ??? ??? ??? ??? ??

?? - - Technology? ??? description ? ??

- ?? ASIC ???? ? ??

?? ??? ???? ?? - ?? ? ?? ?? ( ??

???? ???? ??) - ??? VHDL ??? ??

?????? ??? ?? - ??? ? ??? (rapid

prototyping) ?? - - ?? ?? ??

- ???? ?? ??? ??? ??

?? ??? ??

4

- - ?? HDL ? ??? ??

- IEEE ??? ??? ?? ???

?? HDL - ?????? ?? ? ????

??? ???? ??? - ????? ??

- - ??? ?? ??

- ??? ?? ? ASIC ??

??? ?? VHDL ???? - ??? ?? ? ??? ??

- - ???? ????

- VHDL ???

structured design ??? ??? ?? ??? - ??? ?? ?? ? ??? ??

? ??? ??

IC ?? ?? ??

ASIC (Application Specific IC) ??

?? ?? ?? ??

-???( semi-custom ) ??? -?? ( application

specific ) -?? ?? ?? ( shorter design turnaround

time (DAT) )

5

- 1.3 VHDL? ASIC ?? ??

- ?. ?? ??? ?? ? ?? ??

- ?? ??? ??

- - ASIC??? ??? ??? ???? ????? ??

??, ???, - ??? megafunction ??? ????

- - ?? ?? ?? ??? ???? ????? ??

primitive logic cell? - building block?? ?? ?????? ?????

- - RAM?? ROM? ?? ???? ??? ???? ???

????? - ?? ????? ???? ????

- - ?? ??? ??? ?? ?? ? Multiplexer,

Decoder, Encoder, -

Comparator,

Adder/Subtractor, -

ALU, Multiplier, Lookup

table,

6

- VHDL ??? ???

circuit design with HDL

logic synthesis

?? ?? ???? ?? ??

simulation

7

- VHDL ????? ????

- - VHDL ???? ??? VHDL? ??? ????

??????? - ? VHDL ??? ?????? ???? ?????

???? ?? - ????

- 1) ????? ??? VHDL ????? ?? ??

????. - ?, VHDL ????? ?? ??? ?? ???

??? ?????? - ???? ? ?? critical path, ???

??? ?? ?? ?? ? ?? - ??? ??? ????? ???

? ? ??? VHDL ?? - ? ? ??? ??.

- 2) ????? ??? ?? VHDL code ?? ??

??? ?? ???. - ????? ?? ??? code?

RTL(Register Transfer Level) ??? - ??? ?? tool dependent ??.

-

- 3) ?? ??? ????? ???? ???? ???? ??

??? - ???? ASIC ?? ?? ?? ????? ??

8

- ?. ASIC ?? ????

System Design Partitioning

???? ??? ?? ?? ?? ??? ????? ?? ????, ????? ?? ??

ASIC? ?? ?? ? ??? ASIC? ???? ?? ?? ??? ????? ?? ?

ASIC Block Diagram Specification

VHDL ???, RTL ????? ??? ?? ? ????? Technology

Targeting Synthesis

Logic Design

Logic Simulation

??? ?? ????? Layout ? ?? ?????, ???? ?? ?????? ?

I/O ? ??

Pre and Post-Layout Verification

Prototype ASIC Fabrication Test

9

- ?. ???? ?? ???? ??

Schematic Entry

VHDL Coding

Netlist Generation

RTL Level VHDL Simulation

Gate Level Logic Simulation

Logic Synthesis

A) ??? ??? ?? ???? B) VHDL ??? ??? ????

?? ???

?? ???

10

VHDL ????

- 2. VHDL ????? ??? Coding Issues

- 2.1 4?? VHDL code ?

- - D flip flop, Latch, AND ???, Multiplexer?

?? ??? ??? - VHDL ?? ???? ??? ?? ??? ??? ????? ??.

- ?. D Flip Flop

- entity D_FF is

- port( b, c in bit

- qout out

bit) - end D_FF

- architecture test of D_FF is

- begin

- process

D Q clk

b

qout

c

11

- ?. Latch

- entity D_Latch is

- port(data, enable in

bit - qout out bit)

- end D_Latch

- architecture test of D_Latch is

- begin

- process(data, enable)

- begin

- if (enable 1)

then - qout lt data

- end if

- end process

- end test

D Q Enable

data

qout

enable

12

- ?. 2-?? AND ???

- entity AND2 is

- port( b, c in

bit - and_out out

bit) - end AND2

- architecture test of AND2 is

- begin

- process

- begin

- if (c 1) then

- and_out lt b

- else

- and_out lt 0

- end if

- end process

- end test

b

and_out

c

13

- ?. 2 x 1 Multiplexer

- entity MUX is

- port( b, c, s in

bit - mux_out out

bit) - end MUX

- architecture test of MUX is

- begin

- process

- begin

- case s is

- when 0 lt

mux_out lt b - when 1 lt

mux_out lt c - end case

- end process

- end test

0 1 select

b

mux_out

c

s

?? ?? ?? s? ?? 1? ?? ? ??? ?? ??? ??? ??

??? ?????? ????? ??? ?? ?? ??? ??

?? ???? latch? ????

14

- 2.2 ???? VHDL Coding Issues

- ?. VHDL Types

- - ?? hierarchy ??? ?? ?? ???? ???

netlist? ???? - ? ? ? ????(conversion function)?

??? ??? ???? - entity ??? port ??? ??? std_logic

???(type)? ???? - ?? ??.

- - ???? ???? ???? ??? ??? buffer?

??? ?? - ? ?? ??. ??? ?? ?? signal? ????

??? buffer? - ??? ??? ???? ??? ?? ??.

- entity buf is

- port ( a, b in std_logic

- c out

std_logic ) - end buf

- architecture Behavioral of buf

is - signal c_int std_logic

15

- ?. Signals and Variables

- - ?????? Signal? ?? update ? ? delta

time? ??? Variable? - delay ?? ?? ?? ???.

- - Variable? ??? ?????? ????? ??? ????

??? - ?? ? ?? glitch? ??? ?? ? ??.

- - Variable? ????? ? ??? ?? ??? ????

???? ?? - ?. Priority Encoding Structure

- - ?? if ?? ??? ??? ?? ??? priority

encoding ??? ?? - ??. ???, ?? ??? ???? case ??

????? ??. - VHDL ?? ??? load signal?

?? 8-?? ???? ?????? - ??.

Signal load0? active ? ? bus? ?? 4??? - ???? ??

4??? load ??, signal load1? active - ? ? bus?

?? 4??? ???? ?? 4??? load - ??, ?

??? ??? ???? ??? ??.

load1

load0

MSB LSB

8-?? ???

8-?? BUS

16

Library IEEE use IEEE.std_logic_1164.all use

IEEE.std_logic_unsigned.all entity ld_cnt is

port ( load in

std_logic_vector(1 downto 0)

databus in std_logic_vector(7 downto 0)

clk in std_logic

count out

std_logic_vector(7 downto 0) end ld_cnt

architecture behavior of ld_cnt is signal

int_cnt std_logic_vector(7 downto 0) begin

count lt int_cnt process

begin wait until clk1 and

clkevent if(load 10)

then int_cnt lt databus(7

downto 4) int_cnt(3 downto 0)

elsif (load 01) then

int_cnt lt int_cnt(7 downto 4) databus(3

downto 0) else

int_cnt lt int_cnt 1

end if end process end behavior

17

- ?. ?? ?? Latches

- - ?? ?? Latch? ???? ?? ?? ???? if ??

case ?? - ??? ?? ??? ???? ????? ?? (2.1 ??)

- ?. ???? ???? Resets

- - ??? reset ??? ?? ??? if ??

???(clock statement) ? - ?? ???? ??, ???? reset ??? ?? ???

if ?? ? - ?? ??? ???? ??.

- ??? reset ??? ?? ??? ?

- entity test_reset is

- port ( X, clk, rst

in bit - Z

out bit ) - end test_reset

- architecture behavior of

test_reset is - type state is (S0, S1, S2, S3)

18

- process

- begin

- if rst 0

then - ST

lt S0 - Z

lt 0 - elsif

clkevent and clk 1 then - if X

0 -

then Z lt 0 - else

-

case ST is -

- -

- -

- -

end case - end

if - end process

- end behavior

19

- 3. ?? ????? ?? ?

- - 3???? ?? ????? VHDL ????? ?? ?? LODECAP

- ??? Sample ?? ?? ?? ???? ?????.

- 3.1 ????? ?

- ?. Multiplexer

- Ô 2-way 2 x 1 multiplexer

ltmuxType1.vhdgt - library IEEE

- use IEEE.std_logic_logic_1164.all

- use IEEE.std_logic_signed.all

- entity muxType1 is

- port(a, b IN std_logic_vector(1 downto 0)

- s IN std_logic

- z OUT std_logic_vector(1

downto 0))

2

2

a

2 x 1 MUX

z

2

b

s

20

Ô 2-way 2 x 1 multiplexer

ltmuxType2.vhdgt library IEEE use

IEEE.std_logic_signed.all use

IEEE.std_logic_signed.all entity muxType2 is

port(a, b IN std_logic_vector(1 downto 0)

s IN std_logic z

OUT std_logic_vector(1 downto 0)) end

muxType2 architecture RTL of muxType2 is

signal TMP std_logic_vector(1 downto

0) begin process(a, b, s) begin

if s 0 then z lt a else z lt b

end if end process end RTL

4 x 1 MUX

2

a

z

2

2

b

s

21

?? 1. Muxtype2? ?? ??

22

?? 2. Muxtype2? ????? ??

23

Ô 2-way 4 x

1 multiplexer ltmuxType3.vhdgt library

IEEE use IEEE.std_logic_1164.all use

IEEE.std_logic_signed.all entity muxType3 is

port(a, b, c, d IN std_logic_vector(1

downto 0) s IN

std_logic(1 downto 0) z

OUT std_logic_vector(1 downto 0)) end

muxType3 architecture RTL of muxType3

is begin process(a, b, c, d, s) begin

case s is when 00 gt z lta

when 01 gt z ltb when 10 gt z

ltc when 11 gt z ltd when

others gt z lt00 end case end

process end RTL

24

Ô Enable ?? 4-way 4 x 1

multiplexer ltmux4.vhdgt library IEEE use

IEEE.std_logic_1164.all use IEEE.std_logic_signe

d.all entity MUX4 is port(l0, l1, l2, l3

IN std_logic_vector(3 downto 0)

ENABLE IN std_logic SEL

IN std_logic_vector(1 downto 0)

Y OUT

std_logic_vector(3 downto 0)) end

MUX4 architecture RTL of MUX4 is begin

process ( SEL, ENABLE, l0, l1, l2, l3)

begin if ENABLE 0 then

case SEL is when 00 gt Y lt

l0 when 01 gt Y lt l1

when 10 gt Y lt l2

when othersgt Y lt l3 end case

else Y lt 0000 else

if end

process end RTL

ENABLE

25

?? 3. 4x1 Multiplexer ? ?? ??

26

?? 4. 4x1 Multiplxer? ????? ??

27

?. Decoder ?? Ô 2-to-4 decoder

ltdecoder1.vhdgt library IEEE use

IEEE.std_logic_1164.all use IEEE.std_logic_signe

d.all entity decoder1 is port(a IN

std_logic_vector(1 downto 0) d

OUT std_logic_vector(3 downto 0)) end

decoder1 architecture RTL of decoder1

is begin process begin case a

is when 00 gt d lt 0001

when 01 gt d lt 0010 when 10 gt

d lt 0100 when others gt d lt

1000 end case end process end

RTL

decoder1

2

4

a

d

28

?? 7. Decoder1? ?? ??

?? 8. Decoder1? ????? ??

29

Ô BCD-to-7segment decoder ltBCD_7.vhdgt

y(6)

BCD-to-7 Segment Decoder

G

G

y(5)

F

y(4)

F

B

E

y(3)

A

4

D

y(2)

BCD_data

C

E

C

y(1)

B

D

y(0)

A

library IEEE use IEEE.std_logic_1164.all enti

ty BCD_7 is port(BCD_data IN

std_logic_vector(3 downto 0)

Y OUT std_logic_vector(6 downto

0)) end BCD_7

30

architecture RTL of BCD_7 is begin

process(BCD_data) begin case BCD_data

is when 0000 gt Y lt 1111110

when 0001 gt Y lt 0110000 when

0010 gt Y lt 1101101 when 0011

gt Y lt 1111001 when 0100 gt Y lt

0110011 when 0101 gt Y lt

1011011 when 0110 gt Y lt

1011111 when 0111 gt Y lt

1110000 when 1000 gt Y lt

1111111 when 1001 gt Y lt

1110011 when others gt Y lt

0000000 end case end process end

RTL

31

?? 9. BCD_7? ?? ??

?? 10. BCD_7? ????? ??

32

?. Encoder ?? Ô

ltencoder.vhdgt ?? library IEEE use

IEEE.std_logic_1164.all use IEEE.std_logic_signe

d.all entity encoder is port(a IN

std_logic_vector(3 downto 0) z

OUT std_logic_vector(1 downto 0)) end

encoder architecture RTL of encoder is

begin z lt 00 when a(0) 1 else

01 when a(1) 1 else 10 when a(2)

1 else 11 end RTL

encoder

a(3)

z(1)

a(2)

z(0)

a(1)

a(0)

33

Ô ltfunc2.vhdgt ?? library IEEE use

IEEE.std_logic_1164.all use IEEE.std_logic_signe

d.all entity FUNC2 is port(A, B, C, D

IN std_logic ENC_OUT OUT

std_logic_vector(1 downto 0)) end

FUNC2 architecture RTL of FUNC2 is begin

process(A, B, C, D) begin if D 0

then ENC_OUT lt 00 elsif C 0 then

ENC_OUT lt 01 elsif B 0 then

ENC_OUT lt 10 elsif A 0 then

ENC_OUT lt 11 elsif ENC_OUT lt 00

end if end process end RTL

34

Ô 1-bit Full-Adder ltFA1.vhdgt ?? library

IEEE use IEEE.std_logic_1164.all use

IEEE.std_logic_signed.all entity FA1 is

port( A, B, CIN IN std_logic

SUM,COUT OUT std_logic) end

FA1 architecture RTL of FA1 is begin

process(A, B, CIN) variable TEMP

std_logic_vector(2 downto 0) begin

TEMP A B CIN

case TEMP is when 000 gt SUM lt 0

COUT lt 0 when 001 010 100

gt SUM lt 1 COUT lt 0 when 011

101 110 gt SUM lt 0 COUT lt 1

when 111 gt sum lt 1 COUT lt 1

when others gt SUM lt 0 COUT lt0

end case end process end RTL

35

Ô 9 bit adder ltadder9.vhdgt library

IEEE use IEEE.std_logic_1164.all entity

adder9 is port(cin IN std_logic

a, b IN std_logic_vector(8 downto 0)

sum OUT std_logic_vector(8 downto 0)

cout OUT std_logic) end

adder9 architecture RTL of adder9 is begin

process ( cin, a, b) variable carry

std_logic begin carry cin

for i in 0 to 8 loop sum(i) lt a(i) XOR

b(i) XOR carry carry (carry and

(a(i) XOR b(i))) or (a(i) and b(i)) end

loop cout lt carry end process end

RTL

36

Ô Pipelined adder ?? lt pipeAdder.vhdgt

library IEEE use

IEEE.std_logic_1164.all use

IEEE.std_logic_signed.all entity

pipeAdder is port ( clk

in std_logic inBus

in std_logic_vector(7 downto 0)

outBus out std_logic_vector(8 downto

0)) end pipeAdder

architecture RTL of pipeAdder is

signal reg_a std_logic_vector(7 downto 0)

signal reg_b std_logic_vector(8

downto 0) begin outBus lt

reg_b process ( clk) begin if (

clk 1 and clkevent) then reg_a

lt inBus reg_b lt (0 reg_a)

(0 inBus) end if end process

end RTL

inBus

Reg_a

Reg_b

Out_Bus

37

?? 15. Pipeadder ? ?? ??

38

?? 16. Pipeadder ? ????? ??

39

Ô 4-bit ? ?? ??? ?? lt absdiff.vhdgt

library IEEE use IEEE.std_logic_1164.all us

e IEEE.std_logic_signed.all entity absdiff

is port (a IN std_logic_vector(3 downto

0) b IN std_logic_vector(3

downto 0) d OUT std_logic_vector(3

downto 0)) end absdiff architecture RTL of

absdiff is begin process (a, b) begin

if (a gt b) then d lt a - b else d lt

b - a end if end process end

RTL

40

Ô ALU ?? ltALU.vhdgt

OP1

OP2

8

8

3

ALU

OPCODE

8

ALU_OUT

library IEEE use IEEE.std_logic_1164.all

use IEEE.std_logic_signed.all entity ALU is

port(OPCODE IN std_logic_vector(2 downto

0) OP1,OP2 IN std_logic_vector(7

downto 0) ALU_OUT OUT

std_logic_vector(7 downto 0)) end ALU

41

architecture RTL of ALU is begin process

(OPCODE, OP1, OP2) begin case

OPCODE is when 000 gt

ALU_OUT lt OP1 OP2 when 001 gt

ALU_OUT lt OP1 - 1 when

010 gt ALU_OUT lt OP1 - OP2

when 011 gt ALU_OUT lt OP1

1 when 100 gt ALU_OUT

lt OP1 and OP2 when 101 gt

ALU_OUT lt OP1 or OP2 when 101

gt ALU_OUT lt not OP2

when others gt ALU_OUT lt OP1

end case end process end RTL

42

?? 17. Alu ? ?? ??

43

?? 18. Alu ? ????? ??

44

Ô Increment ?? lt inc.vhdgt

library IEEE use IEEE.std_logic_1164.all use

IEEE.std_logic_signed.all entity INC is

port(PC_ADDR IN std_logic_vector(4 downto

0) INC_ADDR OUT std_logic_vector(4

downto 0)) end INC architecture RTL of INC

is begin INC_ADDR lt PC_ADDR 1 end RTL

45

?? 19. Increment? ?? ??

46

?? 20. Increment? ????? ??

47

Ô Decrement ?? ltdec.vhdgt library

IEEE use IEEE.std_logic_1164.all use

IEEE.std_logic_signed.all entity DEC is

port(PC_ADDR IN std_logic_vector(4 downto

0) DEC_ADDR OUT std_logic_vector(4

downto 0)) end DEC architecture RTL of DEC

is begin DEC_ADDR lt PC_ADDR -1 end RTL

48

3.2 ????? ? ?. ???(counter) Ô

6-bit up counter ?? lt upCount.vhdgt library

IEEE use IEEE.std_logic_1164.all use

IEEE.std_logic_signed.all entity upCount is

port(CLK32M, MRESET in std_logic

upCountOut out

std_logic_vector(5 downto 0)) end

upCount architecture RTL of upCount is signal

TMP std_logic_vector(5 downto 0) begin

upCountOut lt TMP process (CLK32M, MRESET)

begin if MRESET 1 then TMP

lt 000000 elsif (CLK32M 0 and

CLK32Mevent) then TMP lt TMP 1

end if end process end RTL

49

Ô Enable? load? ?? 6-bit up-counter ??

ltupCount2.vhdgt library

IEEE use IEEE.std_logic_1164.all use

IEEE.std_logic_signed.all entity upCount2 is

port( clk, reset, enable, load in

std_logic dataBus

in std_logic_vector(5 downto 0)

upCount2Out out

std_logic_vector(5 downto 0)) end

upCount2 architecture RTL of upCount2

is signal TMP std_logic_vector(5 downto

0) signal clkEnable std_logic begin

upCount2Out lt TMP clkEnable lt clk and

enable process ( clkEnable, reset, load)

begin if reset 1 then TMP lt 000000

elsif ( clkEnable 1 and

clkEnableevent) then if load 1

then TMP lt dataBus else TMP lt TMP

1 end if end if end

process end RTL

50

?? 25. Upcount2 ? ?? ??

51

?? 26. Upcount2 ? ?? ??

52

Ô 6-bit up/down counter ?? lt

upDownCount.vhdgt library IEEE use

IEEE.std_logic_1164.all use IEEE.std_logic_signe

d.all entity upDownCount is port( clk,

reset, up_down, enable, load in std_logic

dataBus in

std_logic_vector(5 downto 0)

count out std_logic_vector(5

downto 0)) end upDownCount architecture RTL

of upDownCount is signal TMP

std_logic_vector(5 downto 0) signal clkEnable

std_logic constant ZERO std_logic_vector

000000 begin count lt TMP

clkEnable lt clk and enable process(

clkEnable, reset, load) begin if reset

1 then TMP lt ZERO elsif ( clkEnable

1 and clkEnableevent) then if load

1 then TMP lt dataBus elsif

up_down 1 then TMP lt TMP 1 else

TMP lt TMP - 1 end if end

if end process end RTL

53

?. Clock ??? Ô Clock 5 ?? ?? lt

clk_gen.vhdgt library IEEE use

IEEE.std_logic_1164.all entity CLK_GEN is

port(CLK, RST IN std_logic

CLK_HOT OUT std_logic_vector(4 downto

0) end CLK_GEN architecture RTL of CLK_GEN

is signal CURRENT_STAT, NEXT_STATE

std_logic_vector(4 downto 0) begin

process(CURRNT_STATE) begin if

CURRENT_STATE 00000 then NEXT_STATE lt

00001 elsif CURRENT_STATE 00001 then

NEXT_STATE lt 00010 elsif CURRENT_STATE

00010 then NEXT_STATE lt 00100 elsif

CURRENT_STATE 00100 then NEXT_STATE lt

01000 elsif CURRENT_STATE 01000 then

NEXT_STATE lt 10000 elsif CURRENT_STATE

10000 then NEXT_STATE lt 00001 else

NEXT_STATE lt 00001 end if end

process process (CLK, RST) begin if

RST 0 then CURRENT lt 00000 elsif CLK

0 and CLKevent then CURRENT_STATE lt

NEXT_STATE end if end process

CLK_HOT lt CURRENT_STATE end RTL

54

?? 31. Clock generator ? ?? ??

55

?? 32. Clock generator ? ????? ??

56

lt RAM ???? ??? gt - address bus8, data

bus8 Modeling Guide - 2?? Memory ???

?? ??. - Address ?? std_logic_vector? Integer?

???? Subprogram ??. - RAM ????? Signal?? ??. -

Chip Disable? Write Mode? ??? Z? ??. library

IEEE use IEEE.std_logic_1164.ALL use

IEEE.std_logic_unsigned.ALL entity RAM is

port ( ADDR in std_logic_vector(0 to 7)

CE_N, RD_N, WR_N in std_logic

DATA inout std_logic(7 downto 0)) end

RAM

57

architecture RTL of RAM is subtype RAM_WORD

is std_logic_vector(7 downto

0) type RAM_TABLE is array(0 to 255) of

RAM_WORD signal RAM_DATA

RAM_TABLE begin process (CE_N,RD_N,WR_N,ADDR)

variable TMP integer begin

DATA lt ZZZZZZZZ TMP

conv_integer(ADDR) if CE_N0 and

RD_N0 then DATA lt RAM_DATA(TMP)

elsif CE_N0 and WR_N0 then

RAM_DATA(TMP) lt DATA end

if end process end RTL

58

lt ROM ???? ??? gt - Address bus3, Data

bus5 Modeling Guide - 2?? Memory ???

?? ??. - Address ?? std_logic_vector? Integer?

???? Subprogram ??. - ROM ????? Constant??

??. - Chip Disable? ?? Z? ??. library IEEE

use IEEE.std_logic_1164.ALL use

IEEE.std_logic_unsigned.ALL entity ROM is

port ( ADDR in std_logic_vector(0 to 2)

CE_N, OE_N in std_logic DATA out

std_logic_vector(4 downto 0)) end ROM

59

architecture RTL of ROM is subtype ROM_WORD

is std_logic_vector(4 downto

0) type ROM_TABLE is array(0 to 7) of

ROM_WORD constant ROM_DATA

ROM_TABLE ROM_ TABLE(

10101, 10000, 11111, 11011,

10001, 01100, 00101, 10011) begin

process (CE_N,OE_N,ADDR) begin if

CE_N0 and OE_N0 then DATA lt

ROM_DATA

(conv_integer(ADDR)) else

DATA lt ZZZZZ end if end

process end RTL

60

Ô Clock ??? ?? ?? ?? ???

ltpgen.vhdgt library IEEE use

IEEE.std_logic_1164.all use IEEE.std_logic_signe

d.all entity pgen is port( clk, reset,

trig in std_logic pulse

OUT std_logic count

OUT std_logic_vector(4 downto

0)) end pgen architecture RTL of pgen

is signal count_TMP std_logic_vector(4 downto

0) signal pulse_TMP std_logic constant

WIDTH std_logic_vector 00111 begin

count lt count_TMP pulse lt pulse_TMP

process ( clk, reset) begin if reset

1 then pulse_TMP lt 0

count_TMP lt 00000 elsif ( clk 1

and clkevent) then if trig 1

then pulse_TMP lt 1 end

if if pulse_TMP 1 then

if count_TMP WIDTH then

pulse_TMP lt 0

61

count_TMP lt count_TMP

else pulse_TMP

lt pulse_TMP count_TMP lt

count_TMP 1 end if else

pulse_TMP lt 0

count_TMP lt 00000 end if end

if end process end RTL

62

?. Memory ?? ?? Ô set? reset? ??

flip-flop ?? ltdff1.vhdgt library IEEE use

IEEE.std_logic_1164.all entity dff1 is port

(set, reset, CLOCK IN std_logic

DIN

IN std_logic q

OUT std_logic_vector(1 downto 0)

qb OUT std_logic) end

dff1 architecture rtl of dff1 is signal TMP

std_logic begin q lt TMP qb lt not

TMP process (clock, DIN, set, reset) begin

if (set 0) then TMP lt 1

elsif (reset 0) then TMP lt 0

elsif(clock 1 and clockevent) then

TMP lt DIN end if end process end

rtl

63

?? 33. D flip flop ? ?? ??

64

?? 34. D flip flop ? ????? ??

65

Ô ??? load? ??? 8 bit register ??

ltregister1.vhdgt library IEEE use

IEEE.std_logic_1164.all entity register1 is

port (ENABLE, LOAD, CLOCK IN std_logic

RESET IN std_logic

REGIN IN std_logic_vector(7

downto 0) LOADDATA IN

std_logic_vector(7 downto 0) REGOUT

OUT std_logic_vector(7 downto

0)) end register1 architecture rtl of

register1 is signal GATEDCLOCK

std_logic begin GATEDCLOCK lt ENABLE and

CLOCK process (GATEDCLOCK, LOAD, RESET,

ENABLE, CLOCK) begin if RESET 0

then REGOUT lt 00000000 elsif

(GATEDCLOCK 0 and GATEDCLOCKevent) then

if LOAD 1 then REGOUT

lt LOADDATA else

REGOUT lt REGIN end if end

if end process end RTL

66

? ? 35. Register1 ? ?? ??

67

? ? 36. Register1 ? ????? ??

68

Ô Left/right?? ??? ??? shift register lt

shiftreg.vhdgt library IEEE use

IEEE.std_logic_1164.all entity shiftreg is

port (ENABLE, LOAD, CLOCK IN std_logic

DIN IN std_logic

REGIN IN

std_logic_vector(7 downto 0) MODE

IN std_logic REGOUT

OUT std_logic_vector (7 downto

0)) end shiftreg architecture rtl of

shiftreg is signal gatedClock

std_logic signal TMP std_logic_vector( 7

downto 0) begin gatedClock lt ENABLE and

CLOCK REGOUT lt TMP begin if (

gatedClock 1 and gatedClockevent) then

if LOAD 1 then TMP lt

REGIN elsif MODE 0 then

TMP lt TMP(6 downto 0) DIN else

TMP lt DIN TMP(7 downto 1)

end if end if end process end

RTL

69

?. FSM(Finite State Machine) - ???

????? ??? ? ????? ???? ???? FSM?? ????

FSM? ????? state transition diagram ?? state

transition table ??? ???? -

FSM? state ??? ???? ???? ??? state ??? ??? ???

? ??? ?? ?? ???? ???? ??? ???? -

FSM? ??? ???? ??? ?? Mealy Machine? Moore

Machine?? ??? ? ?? - Mealy

Machine ????? ??? ??? ??(state)? ??? ?? ??

??

Next state function current

state, inputs Outputs

function current state, inputs

- Moore Machine ????? ??? ??? ???? ??? ???

???? ????

Next state function current

state, inputs Outputs

function current state

70

Inputs

Input Logic

State Memory

Output Logic

Outputs

Current State

Mealy Machine ? VHDL ?? 1

71

Ô Mealy Machine VHDL ?? 1 ltFSM1.vhdgt

library IEEE use

IEEE.std_logic_1164.all entity FSM1 is

port (X, clock in std_logic

Z

out std_logic ) end FSM1

architecture RTL1 of FSM1 is type

state is (S0, S1, S2, S3) signal ST

state begin process

(clock) begin if

clockevent and clock 1 then

if X 0 then Z 0

else case ST is

when S0 gt ST lt S1 Z lt

0 when S1 gt ST lt

S2 Z lt 0 when S2

gt ST lt S3 Z lt 0

when S3 gt ST lt S0 Z lt 1

end case end if

end if end process end

RTL1

72

?? 37. Finite State Machine ? ?? ??

73

?? 38. Finite State Machine ? ????? ??

74

Ô FSM1? ? ?? ??? ?? - ??? ?? FSM? ??? ? ????

??? ???? FSM??? ??? ???? ??(SYNCH)? ???? ??

(COMB)? ?? ? ??? ????? ????? ??? ???? ? ? ? ???

??? ???? ????? ?? ????? ??? ??? ??.

architecture RTL2 of FSM1 is

type ST is (S0, S1, S2, S3) signal

Current_ST, Next_ST state begin

COMB process(Current_ST , X)

begin case Current_ST is

when S0 gt

if X 0 then Z

lt 0 Next_ST lt S0

else Z lt 0

Next_ST lt S1 end if

when S1 gt

if X 0 then

Z lt 0 Next_ST lt S1

else Z lt 0

Next_ST lt S2 end if

75

when S0 gt

if X 0 then

Z lt 0 Next_ST lt S2

else Z lt 0

Next_ST lt S3 end if

when S3 gt

if X 0 then

Z lt 0 Next_ST lt S3

else Z lt 1

Next_ST lt S0 end if

end case SYNCH

process begin wait

until clockevent and clock 1

Current_ST lt Next_ST end

process end RTL2

76

Ô Mealy Machine VHDL ?? 2 ltFSM2.vhd)

reset0

0/0

S0

x/z

0/1

0/0

0/0

1/1

S1

S2

1/0

Library IEEE use IEEE.std_logic_1164.all

entity FSM2 is port (RESET, CLK, X

in std_logic Z

out std_logic) end FSM2

architecture RTL of FSM2 is type STATE

is (S0, S1, S2) signal C_STATE,

N_STATESTATE begin SYNC

process(RESET, CLK) begin

if RESET0 then C_STATE lt

S0

77

elsif CLK0 and CLKevent then

C_STATE ltN_STATE end if end

process COMB process (C_STATE,

X) begin case C_STATE is when

S0 gt Z lt '0' if X0' then

N_STATE lt S0 else

N_STATE lt S1 end if when S1

gt Z lt '0' if X0 then

N_STATE lt S0 else

N_STATE lt S2 end if when S2

gt if X0 then N_STATE lt

SO Z lt 1

78

else N_STATE lt S1

Z lt 1 end if end case

end process end RTL

79

Ô Mealy Machine ?? 3

ltFSM3.vhdgt library IEEE use

IEEE.std_logic_1164.all entity FSM3 is

port(RESET, CLK, X in std_logic

z out

std_logic) end FSM3

architecture RTL of FSM3 is

type STATE is (S0, S1, S2) signal

C_STATE, N_STATE STATE begin SYNC

process (RESET, CLK) begin if RESET

0 then C_STATE lt S0 elsif CLK 0

and CLKevent then C_STATE lt N_STATE end

if end process COMB process (

C_STATE, X) begin case C_STATE is

80

when S0 gt Z lt 0 if X

0 then N_STATE lt S0 else

N_STATE lt S1 end if

when S1 gt Z lt 0 if X 0 then

N_STATE lt S0 else N_STATE lt S2

end if when S2 gt

if X 0 then N_STATE lt S0 Z lt 0

else N_STATE lt S1 Z lt 1

end if end case end process end

RTL

81

Moore Machine? ? Ô ?????? ??

ltWAVEGEN.vhdgt

PH1,PH2,TMP_PH3

RESET0

110

001

010

101

111

011

CLK

PH1

PH2

PH3

82

library IEEE use IEEE.std_logic_1164.all

entity WAVEGEN is port (RESET, CLOCK in

std_logic PH1, PH2, PH3 out

std_logic) end WAVEGEN architecture RTL of

WAVEGEN is constant S0 std_logic_vector(2

downto 0) 110" constant S1

std_logic_vector(2 downto 0) 010

constant S2 std_logic_vector(2 downto 0)

111 constant S3 std_logic_vector(2

downto 0) 011 constant S4

std_logic_vector(2 downto 0) 101

constant S5 std_logic_vector(2 downto 0)

001 signal C_STATE, N_STATE

std_logic_vector(2 downto 0) signal TMP_PH3

std_logic signal PH std_logic_vector(2

downto 0) begin P1 process (RESET, CLOCK)

begin if RESET0' then C_STATE lt

S0 elsif CLOCK 1 and CLOCK'event

then C_STATE lt N_STATE end if

83

end process P1 P2 process (C_STATE) begin

case C_STATE is when S0 gt PH lt S0

N_STATE lt S1 when S1 gt PH lt S1

N_STATE lt S2 when S2 gt PH lt S2

N_STATE lt S3 when S3 gt PH lt S3

N_STATE lt S4 when S4 gt PH lt S4

N_STATE lt S5 when others gt PH lt S5

N_STATE lt S0 end case PH1 lt PH(2)

PH2 lt PH(1) TMP_PH3 lt PH(0) end

process P2 P3 process (CLOCK) begin

if CLOCK0 and CLOCKevent then PH3 lt

TMP_PH3 end if end process P3 end RTL

84

?? 39. Moore Machine ? ??? Wave generator? ?? ??

85

?? 40. Moore Machine ? ??? Wave generator? ?????

??