Cpsr PowerPoint PPT Presentations

All Time

Recommended

Realistic testing is not possible, No chance to fix software during use, ... 'Star Wars' Testing ' ... Very limited opportunities for realistic testing ...

| PowerPoint PPT presentation | free to view

* References FAR Subpart 44.3 Contractors Purchasing Systems Reviews ... Negotiation Techniques Price Analysis / Cost Analysis Writing a Price Negotiation ...

| PowerPoint PPT presentation | free to view

'Star Wars' Today. Current SDI-like programs are ... 'Star Wars' Today ' ... 'Star Wars' Today. One talked-about version does not use space-based weapons: ...

| PowerPoint PPT presentation | free to download

Artful Integration: Interweaving Media, Materials and Practices ... Sponsored by Computer Professionals for Social Responsibility (CPSR) ...

| PowerPoint PPT presentation | free to download

Highly unequal in different geographic regions and social groups ... of the computer science departments polled employed NO women (stats from the CPSR) ...

| PowerPoint PPT presentation | free to view

MOVS restores the original CPSR as well as changing pc. ADD r0,r0,r1. SWI 0x10. SUB r2,r2,r0 ... MOVS pc, lr @ return from handler. gp = general-purpose ...

| PowerPoint PPT presentation | free to download

... locations with ARM's memory map read and written using load-store instructions ... ARM610 (used in Apple Newton) 32-bit addressing, separate CPSR and SPSR ...

| PowerPoint PPT presentation | free to view

... registers can be used for address or data(37 32-bits ... Versatile Register Set(2/2) Where are User Program Mode and System Mode ? CPSR Definition(1/2) ...

| PowerPoint PPT presentation | free to view

Emulate (in software) a coprocessor: That is not physically ... Emulate (in software) an instruction: That is not part of the standard ARM instruction set. ...

| PowerPoint PPT presentation | free to view

We re drowning in information and starving for knowledge. -Rutherford D. Rodgers Topics Defining Risk Risk Management Tools Risk Management Solutions Defining Risk ...

| PowerPoint PPT presentation | free to view

Arquitetura de Sistemas Embarcados Edna Barros (ensb @cin.ufpe.br) Centro de Inform tica UFPE Introdu o a Arquitetura ARM (Advanced RISC Machine) Hist ria do ...

| PowerPoint PPT presentation | free to download

ARM Processor www.clabsys.com

| PowerPoint PPT presentation | free to view

Lecture 3. ARM Instructions Prof. Taeweon Suh Computer Science Education Korea University

| PowerPoint PPT presentation | free to download

... code size * This training module provides an introduction to the ARM7TDMI processor embedded in the AT91 series of microcontroller. we ... 16bit 32bit ...

| PowerPoint PPT presentation | free to view

which executes 32-bit, word-aligned ARM instructions - Thumb state ... MOVS PC, R14_svc. SWI. PC 2. PC 4. MOV PC,R14. BL. Thumb R14_x. ARM R14_x. 23 ...

| PowerPoint PPT presentation | free to download

Contractor Insurance & Pension Center (DCMAC-E) Supplier ... DCMA Hartford. DCMA Long Island. DCMA Maryland. DCMA Philadelphia. DCMA Springfield. DCMA Syracuse ...

| PowerPoint PPT presentation | free to view

Governing the Commons: The Future of Global Internet Administration. An Overview of the Issues ... Shared set of unique names and addresses. Shared root server ...

| PowerPoint PPT presentation | free to download

DOH! Week 7 Presentation (did we skip a week or something... Other static values can be fudged in. Branch ... Hooked up components ...

| PowerPoint PPT presentation | free to view

ARM7TDMI processor The ARM7TDMI processor is a member of the Advanced RISC machine family of general purpose 32-bit microprocessor What does mean ARM7TDMI ?

| PowerPoint PPT presentation | free to download

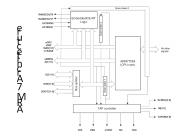

ARM7 Architecture Memory signals MAS[1:0]: bus encodes the size of the transfer. The ARM7TDMI processor can transfer word, alfword, and byte quantities.

| PowerPoint PPT presentation | free to download

What are interrupts ? Stops the execution of main software Redirects the program flow, based on an event, to execute a different software subroutine Interrupt ...

| PowerPoint PPT presentation | free to download

Hazard Detection and Pipeline Stalls. Interrupts. Control. Datapath Construction ... To do so, we create a Mini Program that runs, while stalling the next instruction ...

| PowerPoint PPT presentation | free to view

gpio pxa270 gpio gpio gpio pxa270 gpio

| PowerPoint PPT presentation | free to download

Understanding and navigating the complex regulatory landscape of the cosmetics industry is vital for ensuring product safety, compliance. Get more insights

| PowerPoint PPT presentation | free to download

The ARM Architecture Halfword access and signed halfword/byte accesses were added to the architecture in v4T, this is the reason the offset field is not as flexible ...

| PowerPoint PPT presentation | free to view

Redirects the program flow, based on an event, to execute a ... Debugger Protection. Protect Mode avoids the debugger to start an interrupt. Automatic Vectoring ...

| PowerPoint PPT presentation | free to view

Two separate instruction sets, 32-bit ARM instructions and 16-bit Thumb instructions ... Return with : MOVS pc, lr. Prefetch Abort ...

| PowerPoint PPT presentation | free to view

ACT is a complete environment for testing compliance to the AMBA spec. ... In addition to our partnering with semiconductor companies, ...

| PowerPoint PPT presentation | free to download

William Stallings Computer Organization and Architecture 8th Edition Chapter 12 Processor Structure and Function CPU Structure CPU must: Fetch instructions Interpret ...

| PowerPoint PPT presentation | free to view

beq stop blt less ;if r0 r1 sub r0, r0, r1 ;subtract r1 from r0 bal gcd less sub r1, r1, r0 ; subtract r0 from r1 bal gcd stop ...

| PowerPoint PPT presentation | free to view

ARM7: GBA, iPod. ARM9: NDS, PSP, Sony Ericsson, BenQ. ARM11: ... All instructions are 32-bit wide and word-aligned. Thus, the last two bits of pc are undefined. ...

| PowerPoint PPT presentation | free to download

Title: The ARM Architecture Author: ARM Training Last modified by: Jeff Created Date: 12/11/1995 11:10:42 AM Document presentation format: On-screen Show (4:3)

| PowerPoint PPT presentation | free to view

Arm (Advance RISC Machine) RISC Overview. A large uniform register file ... Arm Overview. Control over both the ALU and shifter ... ARM registers ...

| PowerPoint PPT presentation | free to view

PC-relative to allow position independent code, and allows restricted branch range to jump to nearby addresses. How to access full 32-bit address space?

| PowerPoint PPT presentation | free to download

ARM operating modes and register usage. Exception vector addresses The ARM condition code field ARM condition codes Branch and Branch with Link binary encoding Branch ...

| PowerPoint PPT presentation | free to download

During investigation of the Jan 2000 Alaska Airlines Flight 261 MD-83 accident, ... Joe Bracken, Steve Corrie (ALPA); Al Spain (Jet Blue), Randy Wallace (DL Ret. ...

| PowerPoint PPT presentation | free to view

Title: Author: Jianjian Song Last modified by: song Created Date: 2/23/2004 3:16:40 PM Document presentation format:

| PowerPoint PPT presentation | free to download

Designs the ARM range of RISC processor cores ... to semiconductor partners who fabricate and sell to their customers. ARM does not fabricate silicon itself ...

| PowerPoint PPT presentation | free to view

Title: Author: Jianjian Song Last modified by: song Created Date: 2/23/2004 3:16:40 PM Document presentation format:

| PowerPoint PPT presentation | free to download

Efficient C Code C code Machine code Compiler ucontroller Your C program is not exactly what is executed Machine code is specific to each ucontroller

| PowerPoint PPT presentation | free to download

Title: PowerPoint Presentation Last modified by: Boki i Mica Created Date: 1/1/1601 12:00:00 AM Document presentation format: On-screen Show Other titles

| PowerPoint PPT presentation | free to view

Ch9 Broader Issues

| PowerPoint PPT presentation | free to download

As soon as detected nIRQ set ... If Another detected of same priority, lowest ... Low priority ISR re-enables interrupts. Higher priority ISR reads AIC_IVR ...

| PowerPoint PPT presentation | free to view

ARM Instruction Sets & Programs Outline The ARM processor ARM instruction set Summary The ARM procssor ARM Ltd ARM was originally developed at Acron Computer Limited ...

| PowerPoint PPT presentation | free to view

ARM Instruction Sets & Programs Outline The ARM processor ARM instruction set Summary The ARM procssor ARM Ltd ARM was originally developed at Acron Computer Limited ...

| PowerPoint PPT presentation | free to view

V = ALU operation oVerflowed. Interrupt Disable bits. I = 1, disables the IRQ. ... oVerflow No meaning Result was greater than 31 bits (V= 1') Indicates a ...

| PowerPoint PPT presentation | free to view

Terminology. Big-Endian Bit Ordering left most bit is bit 0, right most bit ... Terminology ... A program that allows the computer to translate assembly language to ...

| PowerPoint PPT presentation | free to view

Identification of. western Canadian wheat classes at different moisture levels using ... Food science, Chemistry, Pharmaceuticals, Animal science ...

| PowerPoint PPT presentation | free to view

Architectural Support for High-level Languages. Thumb Instruction Set ... ARM Acorn RISC Machine (1983 1985) Acorn Computers Limited, Cambridge, England ...

| PowerPoint PPT presentation | free to download

Designs the ARM range of RISC processor cores ... Halfword means 16 bits (two bytes) Word means 32 bits (four bytes) ... All instructions must be halfword aligned ...

| PowerPoint PPT presentation | free to view

B Loop ;repeat forever. aLoop DCD Loop. aPort DCD IOPORT_ADDRESS. END ... 21 00000018 E1A00000 NOP ;do nothing. 22 0000001C EAFFFFF8 B Loop ;repeat forever ...

| PowerPoint PPT presentation | free to view

Chapter 2 Instruction Sets (Slides are taken from the textbook s)

| PowerPoint PPT presentation | free to download

cmp register1, #immediate ;compare register1 with ; immediate number ... Cars make a great vehicle for deploying embedded processors in huge numbers. ...

| PowerPoint PPT presentation | free to download

Filosofia delle scienze cognitive Macchine, Modelli, Spiegazioni David Hilbert Macchine intelligenti Gli antecedenti pi immediati Esiste un algoritmo per ...

| PowerPoint PPT presentation | free to view

Siekmann / Schillo Seminar Geschichte der Informatik Joseph Weizenbaum 8. M rz 2002 Stephan Wiehr Joseph Weizenbaum Gliederung Biographie Zeit am MIT Time-sharing ...

| PowerPoint PPT presentation | free to download

Low-Frequency Pulsar Surveys and Supercomputing. Matthew Bailes. Outline: ... 4 Stokes, umpteen pulsars. Real-time fold to DM=250 pc/cc. O(100) Ops/sample ...

| PowerPoint PPT presentation | free to download