Sprinkler Buddy - PowerPoint PPT Presentation

Title:

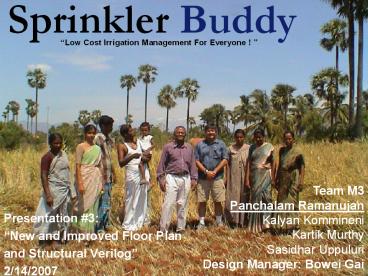

Sprinkler Buddy

Description:

mux21_8 mSiga(sigMuxa,takeShiftSig,{1'b1,siga,3'b000},shOut) ... sbshiftr_8 sbs(shOut,mShiftOut,expDiff); //AddSub significands based on signs ... – PowerPoint PPT presentation

Number of Views:27

Avg rating:3.0/5.0

Title: Sprinkler Buddy

1

Sprinkler Buddy

Low Cost Irrigation Management For Everyone !

Team M3 Panchalam Ramanujan Kalyan

Kommineni Kartik Murthy Sasidhar Uppuluri Design

Manager Bowei Gai

- Presentation 3

- New and Improved Floor Plan

- and Structural Verilog

- 2/14/2007

2

Current Status

- Determine Project ?

- Develop Project Specifications ?

- Plan Architectural Design ?

- Determination of all components in design ?

- Detailed logical flowchart ?

- Design a Floor Plan ?(refined)

- Create Structural Verilog ?

- (All Components done/simulated, tweaking control)

- Make Transistor Level Design and Schematic ?

- Layout ?

- Testing (Extraction, LVS, and Analog Sim.) ?

3

Slightly Revised Transistor

Count

Block ( used) Transistor Count

4020 Muxes (6) 480

6020 Muxes (2) 720

Counter (2) 250

KC ROM (1) 778

P ROM (1) 82

Metric Storage SRAMS (2) 2522

Constant Storage ROM (1) 202

Floating Point Adder (4) 3000

Floating Point Multiplier (2) 2800

10 Bit Registers (9) 140

Datapath Logic / Misc. 2000

Total 31,786

4

Block Size Estimates

Block ( used) Size Estimate (um)

4020 Muxes (4) 20 x 80

6020 Muxes (2) 20 x 120

Counter (2) 12 x 17

KC ROM (4 parts) 181 x 8

P ROM (1) 70 x 8

Metric Storage SRAMS (2) 181 x 60

Constant Storage ROM (1) 181 x 8

Floating Point Adder (4) 100 x 100

Floating Point Multiplier (2) 130 x 130

10 Bit Registers (8) 50 x 10

5

Old (Naïve) Floor Plan

Floor Plan

6

Somewhat Better Floor Plan

7

Current Floor Plan

8

Individual Modules Floating Point Add

Outputs

Will Use Metals 1-4

No Metal 3 below here

Inputs

9

Individual Modules Floating Point Multiply

Inputs

Inputs

Outputs

Outputs

Will Use Metals 1-4

10

Individual Modules Everything Else

Block Metal Layers That Can be Used

4020 Muxes M1 M2

6020 Muxes M1 M2

Counters M1 M2

KC ROM M1 M2 M3 M4

P ROM M1 M2 M3 M4

Metric Storage SRAMS M1 M2 M3 M4

Constant Storage ROM M1 M2 M3 M4

Floating Point Adders M1 M2 M3 M4

Floating Point Multipliers M1 M2 M3 M4

10 Bit Registers M1 M2

11

Metal Directionality

- M1, M2

- Local Connections

- Ground and VDD

- M3,M4

- Clock

- Inside FP Units

- Global Routing

- Control Signals

12

New Design Size

Block ( used) Size Estimate (um)

4020 Muxes (4) 20 x 80

6020 Muxes (2) 20 x 120

Counter (2) 12 x 17

KC ROM (4 parts) 181 x 8

P ROM (1) 70 x 8

Metric Storage SRAMS (2) 181 x 60

Constant Storage ROM (1) 181 x 8

Floating Point Adder (4) 100 x 100

Floating Point Multiplier (2) 130 x 130

10 Bit Registers (8) 50 x 10

- 454um x 450 um

- 1 1 aspect ratio

- .2 mm2 area

- .142 Transistor Density

13

Control Verilog

wire 90 hu_temp,hu_tmax,hu_tmin,hu_tempt

oadd //HU Control Signals wire

hu_tmax_en,hu_tmin_en,hu_mux_sel,hu_add_start,hu_t

emp_en //HU Output Signals wire

hu_add_done,hu_fsm_start,hu_add_sign wire

90 hu_add_out huFSM

_huFSM(hu_tmax_en,hu_tmin_en,hu_mux_sel,hu_add_sta

rt,hu_temp_en, hu_fsm_start,hu_add_si

gn,hu_add_done,clk,rst) not

_hun0(not_g_dclk,g_dclk) and

_huEn(hu_fsm_start,g_hclk,not_g_dclk)

reg_x (10,0) _temp(.q(hu_temp),.d(g_temp),.clk(cl

k),.reset(rst),.en(hu_temp_en)) reg_x

(10,10'b0011110001) _tmax(.q(hu_tmax),.d(hu_temp)

,.clk(clk),.reset(rst),.en(hu_tmax_en))

reg_x (10,10'b0011110001) _tmin(.q(hu_tmin),.d(hu

_temp),.clk(clk),.reset(rst),.en(hu_tmin_en))

mux21_10 _huMux(.out(hu_temptoadd),.sel(hu_mu

x_sel),.a(hu_tmax),.b(hu_tmin)) fpadder

_fpahr(.out(hu_add_out),.done(hu_add_done),.a(hu_t

emp),.b(hu_temptoadd),

.addSub(1'b1),.start(hu_add_start),.clk(clk),.rst(

rst)) assign hu_add_signhu_add_out9

14

Multiplier Verilog

wire signa,signb,cout1,cout2

//Assign pieces of Inputs assign signa

a9 assign signb b9 assign

expa a84 assign expb b84

assign siga a30 assign sigb

b30 //Calculate Exponent

addSub_6 ab(preExp,cout1,1'b0,expa,1'b0,expb,1

'b0) addSub_6 ba(postExp,cout2,preExp,6'b

001111,1'b1) //Calculate Significand

uMult_5 um(postSig,1'b1,siga,1'b1,sigb)

//Normalize fpmultnormalize

nm(postNormSig,postNormExp,postSig,postExp)

//Assign Final Output assign

out84postNormExp40 assign

out30postNormSig xor

msign(out9,signa,signb) endmodule

//modify if rounding later,combine adders

later module fpmultnormalize(sigPostNorm,expPost

Norm,sigPreNorm,expPreNorm) output

30 sigPostNorm output 50

expPostNorm input 90 sigPreNorm

input 50 expPreNorm wire cout

wire 50 addAmnt //Adjust

Significand mux21_4 mm(sigPostNorm,sigPreN

orm9,sigPreNorm74,sigPreNorm85)

//Adjust Exponent mux21_6

mm5(addAmnt,sigPreNorm9,6'b000000,6'b000001)

//reduce me later addSub_6

as5(expPostNorm,cout,expPreNorm,addAmnt,1'b1)

endmodule

15

Adder Verilog

module fpAddSigUnit(sigFinal,siga,sigb,expDiff,co

mpExpab,clk,rst,takeShiftSig,signa,signb,compSigab

,sRaEn,sRbEn) output 80 sigFinal

output compSigab input 30

siga,sigb input 30 expDiff

input compExpab,takeShiftSig,sRaEn,sRbEn,clk,rst,s

igna,signb wire compSigab,addSub,coutFin

al wire 70 sigFinala,sigFinalb,sigMuxa

,sigMuxb,shOut,mShiftOut wire 90

sigPreOut,sigFinOut //q,d,clk,rst,en

//Choose to register original or shifted sig

mux21_8 mSiga(sigMuxa,takeShiftSig,1'b1,si

ga,3'b000,shOut) mux21_8

mSigb(sigMuxb,takeShiftSig,1'b1,sigb,3'b000,shOu

t) reg_x (8,0) sRa(sigFinala,sigMuxa,clk

,rst,sRaEn(takeShiftSig(compExpab)) )

reg_x (8,0) sRb(sigFinalb,sigMuxb,clk,rst,sRbEn(

takeShiftSigcompExpab) ) //Choose

Significand to shift and shift it //0-gt b

is bigger, 1-gt a is bigger mux21_8

mshift(mShiftOut,compExpab,sigFinala,sigFinalb)

sbshiftr_8 sbs(shOut,mShiftOut,expDiff)

//AddSub significands based on signs

//10 bit adder to accomodate negative bit and

adding secret bits comp8

c8(compSigab,sigMuxa,sigMuxb) xor

x0(addSub,signa,signb) addSub_10

addSigs(sigPreOut,coutFinal,2'b00,sigMuxa,2'b00

,sigMuxb,addSub)

16

Design Challenges and Implementation

DecisionsFor The Past Week

Design Challenge Translation to HW

Low Power Design Ripple Carry Adder Quiet Bit Line SRAM Architecture Sense Amplifier Flip Flop

17

Quiet-Bitline Architecture for SRAM

- No Pre-Charging

- One side driving scheme where only a strong 0

is forced in bit or bit bar when writing - 85 power reduction over traditional methods

Citation A Low-Power SRAM Design Using

Quiet-Bitline Architecture by Cheng et. al.

18

Problems/Questions

- Our Floor plan has a hole in the top right

- Need to more accurately determine timing delays

through modules

19

For Next Week

- Make Transistor Level Schematic

- Begin Layout of Smaller Modules

- Continue to Revise and Update Floor Plan