Comparison of Latches and Flip-Flops PowerPoint PPT Presentation

1 / 50

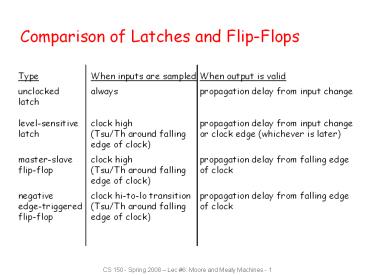

Title: Comparison of Latches and Flip-Flops

1

Comparison of Latches and Flip-Flops

Type When inputs are sampled When output is

valid unclocked always propagation delay from

input changelatch level-sensitive clock

high propagation delay from input

changelatch (Tsu/Th around falling or clock edge

(whichever is later) edge of clock) master-slave

clock high propagation delay from falling

edgeflip-flop (Tsu/Th around falling of

clock edge of clock) negative clock hi-to-lo

transition propagation delay from falling

edgeedge-triggered (Tsu/Th around falling of

clockflip-flop edge of clock)

2

Typical Timing Specifications

- Positive edge-triggered D flip-flop

- Setup and hold times

- Minimum clock width

- Propagation delays (low to high, high to low, max

and typical)

all measurements are made from the clocking event

that is, the rising edge of the clock

3

Cascading Edge-triggered Flip-Flops

- Shift register

- New value goes into first stage

- While previous value of first stage goes into

second stage - Consider setup/hold/propagation delays (prop must

be gt hold)

100

IN Q0 Q1 CLK

4

Cascading Edge-triggered Flip-Flops

- Shift register

- New value goes into first stage

- While previous value of first stage goes into

second stage - Consider setup/hold/propagation delays (prop must

be gt hold)

Clk1

Delay

100

IN Q0 Q1 CLK

Clk1

5

Cascading Edge-triggered Flip-Flops (contd)

- Why this works

- Propagation delays exceed hold times

- Clock width constraint exceeds setup time

- This guarantees following stage will latch

current value before it changes to new value

In Q0 Q1 CLK

Tsu 4ns

Tsu 4ns

timing constraints guarantee proper operation

of cascaded components

Tp 3ns

Tp 3ns

assumes infinitely fast distribution of the clock

Th 2ns

Th 2ns

6

Clock Skew

- The problem

- Correct behavior assumes next state of all

storage elementsdetermined by all storage

elements at the same time - Difficult in high-performance systems because

time for clock to arrive at flip-flop is

comparable to delays through logic (and will soon

become greater than logic delay) - Effect of skew on cascaded flip-flops

100

In Q0 Q1 CLK0 CLK1

CLK1 is a delayed version of CLK0

original state IN 0, Q0 1, Q1 1 due to

skew, next state becomes Q0 0, Q1 0, and not

Q0 0, Q1 1

7

Summary of Latches and Flip-Flops

- Development of D-FF

- Level-sensitive used in custom integrated

circuits - can be made with 4 switches

- Edge-triggered used in programmable logic devices

- Good choice for data storage register

- Historically J-K FF was popular but now never

used - Similar to R-S but with 1-1 being used to toggle

output (complement state) - Good in days of TTL/SSI (more complex input

function D JQ' K'Q - Not a good choice for PLAs as it requires two

inputs - Can always be implemented using D-FF

- Preset and clear inputs are highly desirable on

flip-flops - Used at start-up or to reset system to a known

state

8

Flip-Flop Features

- Reset (set state to 0) R

- Synchronous Dnew R' Dold (when next clock

edge arrives) - Asynchronous doesn't wait for clock, quick but

dangerous - Preset or set (set state to 10 S (or sometimes

P) - Synchronous Dnew Dold S (when next clock

edge arrives) - Asynchronous doesn't wait for clock, quick but

dangerous - Both reset and preset

- Dnew R' Dold S (set-dominant)

- Dnew R' Dold R'S (reset-dominant)

- Selective input capability (input enable/load)

LD or EN - Multiplexer at input Dnew LD' Q LD Dold

- Load may/may not override reset/set (usually R/S

have priority) - Complementary outputs Q and Q'

9

Registers

- Collections of flip-flops with similar controls

and logic - Stored values somehow related (e.g., form binary

value) - Share clock, reset, and set lines

- Similar logic at each stage

- Examples

- Shift registers

- Counters

10

Shift Register

- Holds samples of input

- Store last 4 input values in sequence

- 4-bit shift register

11

Shift Register Verilog

module shift_reg (out4, out3, out2, out1, in,

clk) output out4, out3, out2, out1 input

in, clk reg out4, out3, out2, out1 always

_at_(posedge clk) begin out4 lt out3 out3

lt out2 out2 lt out1 out1 lt in

end endmodule

12

Shift Register Verilog

module shift_reg (out, in, clk) output 41

out input in, clk reg 41

out always _at_(posedge clk) begin out lt

out31, in end endmodule

13

Universal Shift Register

- Holds 4 values

- Serial or parallel inputs

- Serial or parallel outputs

- Permits shift left or right

- Shift in new values from left or right

clear sets the register contentsand output to

0s1 and s0 determine the shift function

s0 s1 function 0 0 hold state 0 1 shift

right 1 0 shift left 1 1 load new input

14

Design of Universal Shift Register

- Consider one of the four flip-flops

- New value at next clock cycle

Nth cell

to N-1th cell

to N1th cell

Q

D

CLK

CLEAR

clear s0 s1 new value 1 0 0 0 0 output 0 0

1 output value of FF to left (shift

right) 0 1 0 output value of FF to right (shift

left) 0 1 1 input

s0 and s1control mux

QN-1(left)

QN1(right)

InputN

15

Universal Shift Register Verilog

module univ_shift (out, lo, ro, in, li, ri, s,

clr, clk) output 30 out output lo, ro

input 30 in input 10 s input li,

ri, clr, clk reg 30 out assign lo

out3 assign ro out0 always _at_(posedge clk

or clr) begin if (clr) out lt 0 else

case (s) 3 out lt in 2 out lt

out20, ri 1 out lt li, out31

0 out lt out endcase end endmodule

16

Shift Register Application

- Parallel-to-serial conversion for serial

transmission

parallel outputs

parallel inputs

serial transmission

17

Pattern Recognizer

- Combinational function of input samples

- In this case, recognizing the pattern 1001 on the

single input signal

18

Counters

- Sequences through a fixed set of patterns

- In this case, 1000, 0100, 0010, 0001

- If one of the patterns is its initial state (by

loading or set/reset) - Mobius (or Johnson) counter

- In this case, 1000, 1100, 1110, 1111, 0111, 0011,

0001, 0000

19

Binary Counter

- Logic between registers (not just multiplexer)

- XOR decides when bit should be toggled

- Always for low-order bit, only when first bit is

true for second bit, and so on

20

Binary Counter Verilog

module shift_reg (out4, out3, out2, out1, clk)

output out4, out3, out2, out1 input in, clk

reg out4, out3, out2, out1 always _at_(posedge

clk) begin out4 lt (out1 out2 out3)

out4 out3 lt (out1 out2) out3 out2

lt out1 out2 out1 lt out1 1b1

end endmodule

21

Binary Counter Verilog

module shift_reg (out4, out3, out2, out1, clk)

output 41 out input in, clk reg

41 out always _at_(posedge clk) out lt out

1 endmodule

22

Four-bit Binary Synchronous Up-Counter

- Standard component with many applications

- Positive edge-triggered FFs w/ sync load and

clear inputs - Parallel load data from D, C, B, A

- Enable inputs must be asserted to enable

counting - RCO ripple-carry out used for cascading counters

- high when counter is in its highest state 1111

- implemented using an AND gate

(2) RCO goes high

(3) High order 4-bits are incremented

(1) Low order 4-bits 1111

23

Offset Counters

- Starting offset counters use of synchronous

load - e.g., 0110, 0111, 1000, 1001, 1010, 1011, 1100,

1101, 1111, 0110, . . . - Ending offset counter comparator for ending

value - e.g., 0000, 0001, 0010, ..., 1100, 1101, 0000

- Combinations of the above (start and stop value)

24

Sequential Logic Summary

- Fundamental building block of circuits with state

- Latch and flip-flop

- R-S latch, R-S master/slave, D master/slave,

edge-triggered D FF - Timing methodologies

- Use of clocks

- Cascaded FFs work because prop delays exceed hold

times - Beware of clock skew

- Basic registers

- Shift registers

- Pattern detectors

- Counters

25

Sequential Logic Implementation

- Models for representing sequential circuits

- Finite-state machines (Moore and Mealy)

- Representation of memory (states)

- Changes in state (transitions)

- Design procedure

- State diagrams

- State transition table

- Next state functions

26

Abstraction of State Elements

- Divide circuit into combinational logic and state

- Localize feedback loops and make it easy to break

cycles - Implementation of storage elements leads to

various forms of sequential logic

27

Forms of Sequential Logic

- Asynchronous sequential logic state changes

occur whenever state inputs change (elements may

be simple wires or delay elements) - Synchronous sequential logic state changes

occur in lock step across all storage elements

(using a periodic waveform - the clock)

28

Finite State Machine Representations

- States determined by possible values in

sequential storage elements - Transitions change of state

- Clock controls when state can change by

controlling storage elements - Sequential Logic

- Sequences through a series of states

- Based on sequence of values on input signals

- Clock period defines elements of sequence

29

Example Finite State Machine Diagram

- Combination lock

30

Can Any Sequential System be Represented with a

State Diagram?

- Shift Register

- Input value shownon transition arcs

- Output values shownwithin state node

31

Counters are Simple Finite State Machines

- Counters

- Proceed thru well-defined state sequence in

response to enable - Many types of counters binary, BCD, Gray-code

- 3-bit up-counter 000, 001, 010, 011, 100, 101,

110, 111, 000, ... - 3-bit down-counter 111, 110, 101, 100, 011,

010, 001, 000, 111, ...

32

Verilog Upcounter

module binary_cntr (q, clk) inputs clk

outputs 20 q reg 20 q reg

20 p always _at_(q)

//Calculate next state case (q) 3b000

p 3b001 3b001 p 3b010

3b111 p 3b000 endcase always

_at_(posedge clk) //next becomes current state

q lt p endmodule

33

How Do We Turn a State Diagram into Logic?

- Counter

- Three flip-flops to hold state

- Logic to compute next state

- Clock signal controls when flip-flop memory can

change - Wait long enough for combinational logic to

compute new value - Don't wait too long as that is low performance

34

FSM Design Procedure

- Start with counters

- Simple because output is just state

- Simple because no choice of next state based on

input - State diagram to state transition table

- Tabular form of state diagram

- Like a truth-table

- State encoding

- Decide on representation of states

- For counters it is simple just its value

- Implementation

- Flip-flop for each state bit

- Combinational logic based on encoding

35

FSM Design Procedure State Diagram to Encoded

State Transition Table

- Tabular form of state diagram

- Like a truth-table (specify output for all input

combinations) - Encoding of states easy for counters just use

value

36

Implementation

- D flip-flop for each state bit

- Combinational logic based on encoding

notation to show function represent input to D-FF

N1 C1' N2 C1C2' C1'C2 C1 xor C2 N3

C1C2C3' C1'C3 C2'C3 C1C2C3' (C1'

C2')C3 (C1C2) xor C3

37

Implementation (cont'd)

- Programmable Logic Building Block for Sequential

Logic - Macro-cell FF logic

- D-FF

- Two-level logic capability like PAL (e.g., 8

product terms)

38

Another Example

- Shift Register

- Input determines next state

N1 In N2 C1 N3 C2

39

More Complex Counter Example

- Complex Counter

- Repeats five states in sequence

- Not a binary number representation

- Step 1 Derive the state transition diagram

- Count sequence 000, 010, 011, 101, 110

- Step 2 Derive the state transition table from

the state transition diagram

note the don't care conditions that arise from

the unused state codes

40

More Complex Counter Example (contd)

- Step 3 K-maps for Next State Functions

C A B B' A'C' A BC'

41

Self-Starting Counters (contd)

- Re-deriving state transition table from don't

care assignment

42

Self-Starting Counters

- Start-up States

- At power-up, counter may be in an unused or

invalid state - Designer must guarantee it (eventually) enters a

valid state - Self-starting Solution

- Design counter so that invalid states eventually

transition to a valid state - May limit exploitation of don't cares

- Reset line

- Input which ALWAYS puts counter in a known state

43

State Machine Model

- Values stored in registers represent the state of

the circuit - Combinational logic computes

- Next state

- Function of current state and inputs

- Outputs

- Function of current state and inputs (Mealy

machine) - Function of current state only (Moore machine)

44

State Machine Model (contd)

- States S1, S2, ..., Sk

- Inputs I1, I2, ..., Im

- Outputs O1, O2, ..., On

- Transition function Fs(Si, Ij)

- Output function Fo(Si) or Fo(Si, Ij)

45

Example Ant Brain (Ward, MIT)

- Sensors L and R antennae, 1 if in touching

wall - Actuators F - forward step, TL/TR - turn

left/right slightly - Goal find way out of maze

- Strategy keep the wall on the right

46

Ant Brain

47

Ant Behavior

A Following wall, touching Go forward,

turning left slightly. If R and not L, go to

A If R and L , go to E else go to B

B Following wall, not touching Go forward,

turning right slightly if R, go to A if not

R, go to C

C Break in wall Go forward, turning right

slightly if R, go to A if not R, stay in C

E Wall in front or on left Turn left

If L or R, stay in E Otherwise, go to B

LOST Forward until we touch something

48

Designing an Ant Brain

- State Diagram

49

Synthesizing the Ant Brain Circuit

- Encode States Using a Set of State Variables

- Arbitrary choice - may affect cost, speed

- Use Transition Truth Table

- Define next state function for each state

variable - Define output function for each output

- Implement next state and output functions using

combinational logic - 2-level logic (ROM/PLA/PAL)

- Multi-level logic

- Next state and output functions can be optimized

together

50

Transition Truth Table

- Using symbolic statesand outputs

51

Synthesis

- 5 states at least 3 state variables required

(X, Y, Z) - State assignment (in this case, arbitrarily

chosen)

LOST - 000 E - 001 A - 010 B - 011 C - 100

state L R next state outputs X,Y,Z X', Y',

Z' F TR TL 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0

1 1 0 0 ... ... ... ... ... 0 1 0 0 0 0 1

1 1 0 1 0 1 0 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0

1 1 0 1 0 1 0 1 1 0 0 1 1 0 1 0 1 1 0 0 1 0

0 1 1 0 0 1 1 0 1 0 1 0 1 1 0 ... ... ... ... ...

it now remainsto synthesizethese 6 functions

52

Synthesis of Next State and Output Functions

state inputs next state outputs X,Y,Z L

R X,Y,Z F TR TL 0 0 0 0 0 0 0 0 1 0 0 0 0

0 - 1 0 0 1 1 0 0 0 0 0 1 - 0 0 1 1 0 0 0 0

1 0 0 0 1 1 0 0 1 0 0 1 - 1 0 1 0 0 0 1 0 0

1 1 - 0 1 0 0 0 1 0 1 0 0 0 0 1 1 1 0 1 0 1

0 0 1 0 1 0 1 0 1 0 1 0 1 - 0 0 1 1 0 1 0 1

1 - 0 1 0 0 1 1 0 0 1 1 - 1 0 1 0 1 1 0 1 0

0 - 0 1 0 0 1 1 0 1 0 0 - 1 0 1 0 1 1 0

- e.g.

- TR X Y Z

- X X R Y Z R R TR

53

Circuit Implementation

- Outputs are a function of the current state only

- Moore machine

54

Verilog Sketch

module ant_brain (F, TR, TL, L, R) inputs

L, R outputs F, TR, TL reg X, Y,

Z assign F function(X, Y, Z, L, R)

assign TR function(X, Y, Z, L, R) assign TL

function(X, Y, Z, L, R) always _at_(posedge

clk) begin X lt function (X, Y, Z, L,

R) Y lt function (X, Y, Z, L, R) Z

lt function (X, Y, Z, L, R) end endmodule

55

Dont Cares in FSM Synthesis

- What happens to the "unused" states (101, 110,

111)? - Exploited as don't cares to minimize the logic

- If states can't happen, then don't care what the

functions do - if states do happen, we may be in trouble

Ant is in deep trouble if it gets in this state

56

State Minimization

- Fewer states may mean fewer state variables

- High-level synthesis may generate many redundant

states - Two state are equivalent if they are impossible

to distinguish from the outputs of the FSM, i.

e., for any input sequence the outputs are the

same - Two conditions for two states to be equivalent

- 1) Output must be the same in both states

- 2) Must transition to equivalent states for all

input combinations

57

Ant Brain Revisited

- Any equivalent states?

58

Ant Brain Revisited

Inequivalent since actions differ

Potentially Equivalent (actions equivalent)

59

Equivalence Proof

Equivalent Behavior under R

L R

L R

LOST (F)

E(TL)

A (TL, F)

L

L R

R

L R

L R

R

L R

B (TR, F)

C(TR, F)

R

R

Equivalent Behavior under R

60

New Improved Brain

- Merge equivalent B and C states

- Behavior is exactly the same as the 5-state brain

- We now need only 2 state variables rather than 3

61

New Brain Implementation

62

Sequential Logic Implementation Summary

- Models for representing sequential circuits

- Abstraction of sequential elements

- Finite state machines and their state diagrams

- Inputs/outputs

- Mealy, Moore, and synchronous Mealy machines

- Finite state machine design procedure

- Deriving state diagram

- Deriving state transition table

- Determining next state and output functions

- Implementing combinational logic