Multicycle PowerPoint PPT Presentations

All Time

Recommended

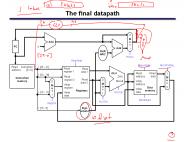

Multicycle Datapath As an added bonus, we can eliminate some of the extra hardware from the single-cycle datapath. We will restrict ourselves to using each functional ...

| PowerPoint PPT presentation | free to download

Instruction Decode and ... based on the instruction type are set b/c control logic busy 'decoding' ... during each step of fetch/decode/execute cycles ...

| PowerPoint PPT presentation | free to download

2001-2003 Howard Huang ... My office hours, move to Mon or Wed? Plan: Pipelining this and next week, maybe performance analysis

| PowerPoint PPT presentation | free to download

Title: PowerPoint Presentation Last modified by: lenovo Created Date: 1/1/1601 12:00:00 AM Document presentation format: (4:3) Other titles

| PowerPoint PPT presentation | free to download

Completion of DLX EX stage floating point arithmetic operations in one or two cycles is impractical since it requires: A much longer CPU clock cycle, and/or

| PowerPoint PPT presentation | free to download

Decode Instruction and Access the Data. from Registers. 3. Perform the Instruction ... Sk denotes that S decodes to k. Load Word & Store Word ( I type ) ...

| PowerPoint PPT presentation | free to view

Address computation for memory access. R-Type instruction execution ... Instruction Decode/Register Fetch/Branch Target. Read/Write. Addr. Memory. IR. Registers ...

| PowerPoint PPT presentation | free to view

PC. Inst Memory. cmp. mux. Reg File. Reg File. Reg File. Arithmetic & Logical. Load. Store ... PC. Next PC. IR. Inst. Mem. Time. A. B. E. Logical immed ...

| PowerPoint PPT presentation | free to view

What did we talk about last class? Have you seen anything interesting in the news? ... approach and many of you gave the answer I was looking for, better parallelism. ...

| PowerPoint PPT presentation | free to download

Multi-Cycle Processor. Stage 0 Instruction Fetch. Stage 1 - Decode. Stage 2 - Execution ... Carry Look Ahead Equations. Generate: gi = (ai and bi) Propagate: ...

| PowerPoint PPT presentation | free to view

The control unit is responsible for producing all of the control ... But it requires a little cleverness... Stage 1 involves instruction fetch and PC increment. ...

| PowerPoint PPT presentation | free to view

This presentation uses powerpoint animation: please viewshow. CWRU EECS 318 ... ( hardwired control ) Multi-cycle using Finite State Machine. CWRU EECS 318 ...

| PowerPoint PPT presentation | free to view

Midterm is on October 12. Allen Parish's help session Friday 10:15-12:15 ... Recall: Marrying two Datapaths. What kind of instructions can be realized by these ...

| PowerPoint PPT presentation | free to download

hold output of that unit until value is used in next clock cycle ... Drain ( ) Drain (-) Source ( ) Source (-) Current Flow. CMOS Circuits. Simple. Avoids difficulties ...

| PowerPoint PPT presentation | free to download

ECE 4436. ECE 5367. Multi-cycle Datapath. ECE 4436. ECE 5367. Single Cycle Review. S. h. i ... What are some of the main steps in the instruction execution? ...

| PowerPoint PPT presentation | free to view

Reading sources from the register file. Performing an ALU ... back to the register file. ... the register file (for arithmetic operations), a constant 4 (to ...

| PowerPoint PPT presentation | free to view

Determinism: all state registers must be deterministic ... (SELF '') Flow Conditions. condSTDEC = STEX . STM1 . STA1 . STDIV. Fetch. Decode. EX. M1 ...

| PowerPoint PPT presentation | free to download

A Multicycle Datapath

| PowerPoint PPT presentation | free to view

EEM 486. EEM 486: Computer Architecture. Lecture 4. Designing a ... ALUOut A SExt(Im16) Step 4. Memory access. MDR Memory[ALUOut] Step 5. Load completion ...

| PowerPoint PPT presentation | free to view

One Hot Encoding. E.g. 4 states need 4 flip flops. ... 10000. 10000. 71. 10000. number of gates. 93. 97. 82. 98. Conclusion. Thank You! Questions? ...

| PowerPoint PPT presentation | free to download

Show any necessary modifications in the multicycle datapath and control figures ... We have to get the second operand from memory before activating the ALU. ...

| PowerPoint PPT presentation | free to download

A specification methodology. appropriate if hundreds of opcodes, modes, cycles, etc. ... Distinction between specification and implementation is sometimes blurred ...

| PowerPoint PPT presentation | free to view

S = A SExt(Im16); MEM[S] = B PC = PC 4. Exec. Reg. File. Mem. Access. Data ... else PC =PC 4 {SExt(Im16),2b0} A. B. E. Time. CS 152 L09 Multicycle (19 ) ...

| PowerPoint PPT presentation | free to download

overkill when ISA matches datapath 1-1. sequencer. control ... ( microprogramming is overkill when ISA matches datapath 1-1) Motivation for Microprogramming ...

| PowerPoint PPT presentation | free to view

S = A SExt(Im16); MEM[S] = B PC = PC 4. Exec. Reg. ... else PC =PC 4 {SExt(Im16),2'b0} A. B. E. Time. CS 152 L09 Multicycle (16 ) Fall 2004 UC Regents ...

| PowerPoint PPT presentation | free to view

Fetch instruction from memory and increment PC ... Instruction Decode and reg fetch. Do not know what instruction is until the end of this step ...

| PowerPoint PPT presentation | free to view

Acyclic. Combinational. Logic (A) storage element. storage element. Acyclic. Combinational. Logic (B) CS152. Lec10.14. Basic Limits on Cycle Time. Next address logic ...

| PowerPoint PPT presentation | free to view

Use the information we've accumulated to specify a finite state machine ... class, FSM returns to the initial state to begin fetching the next instruction ...

| PowerPoint PPT presentation | free to view

The state digrams that arise define the controller for ... cond. next address. 1. dst. src. alu. D. E. C. D. E. C. Branch Jump. Register Xfer Operation. CS152 ...

| PowerPoint PPT presentation | free to view

241-440 Computer System Design Lecture 6 Wannarat Suntiamorntut Part I: Data Path (Multicycle) What s wrong when CPI=1 Memory access time Physics Use hierarchy of ...

| PowerPoint PPT presentation | free to download

Multicycle Registers. Instruction register (IR): hold the instruction during its execution ... The control unit for our multicycle datapath will be a state machine ...

| PowerPoint PPT presentation | free to download

Title: Multicycle datapath Subject: CS232 @ UIUC Author: Howard Huang Description 2001-2003 Howard Huang Last modified by: Oskin Mark Created Date

| PowerPoint PPT presentation | free to download

Multicycle operations. Multiple operations per cycle. Pipelined data paths ... Multicycle Operations. oi. operation. di. delay. for 1 j s, 1 k m. for all oi ...

| PowerPoint PPT presentation | free to view

Technical University of Denmark. Richard Petersens Plads, Building ... Multiply is a multicycle operation [M-1] High-Level Synthesis. 21. SoC-MOBINET courseware ...

| PowerPoint PPT presentation | free to download

Idea behind multicycle approach. We define each instruction from the ISA perspective (do this! ... Result: Our book's multicycle Implementation! 12. 2004 ...

| PowerPoint PPT presentation | free to download

Two-bit predictors are even better (Branch prediction is a hot research topic) ... 10 multicycle functional units in the 'Central' processor ...

| PowerPoint PPT presentation | free to view

Cycle 1. Cycle 2. Fall 2006. 331 W12.3. Multicycle Advantages & Disadvantages ... Cycle 1. Multiple Cycle Implementation: IFetch. Dec. Exec ... Cycle 1. Cycle 2 ...

| PowerPoint PPT presentation | free to view

ECE 426 - VLSI System Design Lecture 9 - ASM Diagrams February 26, 2003 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042

| PowerPoint PPT presentation | free to view

Multi-cycle Approach Dr. Iyad Jafar Adapted from Dr. Gheith Abandah s http://www.abandah.com/gheith/Courses/CPE335_S08/index.html

| PowerPoint PPT presentation | free to download

Chapter 5 The Processor: Datapath and Control

| PowerPoint PPT presentation | free to view

Instruction decode and register fetch. Information available: PC, instruction ... type from address. Use polled exceptions. Use Cause register. This is what ...

| PowerPoint PPT presentation | free to download

Computer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 5: Processor: Datapath & Control We have discussed: Performance Instruction Sets ...

| PowerPoint PPT presentation | free to download

goal is to reduce number of instructions executed ... WrEn. 32. Adr. Data. Memory. MemWr. ALU. Equal. Instruction 31:0 0. 1. 0. 1. 0. 1 21:25 16:20 ...

| PowerPoint PPT presentation | free to download

Fishtail, RealIntent, Atrenta, BluePearl. Some claim specialized FPV engines ... http://www.fishtail-da.com/ http://www.realintent.com ...

| PowerPoint PPT presentation | free to download

Title: The Processor: Datapath & Control Subject: Computer Organization & Design Author: Dr. Bassam Kahhaleh Last modified by: Bassam Kahhaleh Created Date

| PowerPoint PPT presentation | free to view

Instruction-Level Parallelism Review of Pipelining (the laundry analogy) Instruction-Level Parallelism Review of Pipelining (Appendix A) Instruction-Level Parallelism ...

| PowerPoint PPT presentation | free to download

Unconditional Branch. Load/store. Develop datapath modules (RF, ALU, Memory, SignExt) ... All instructions take one cycle (CPI = 1) Cycle time dictated by ...

| PowerPoint PPT presentation | free to view

fetch: PCnext, CacheFetch, PC 4 # State 0 (start) PC 4imm, mPCdisp1 # State 1 ... Examples of exceptions (things that can go wrong) ...

| PowerPoint PPT presentation | free to download

... flops: state changes only on a clock edge, the other inputs determine the new state ... Output changes only on the clock edge. Master-slave structure ...

| PowerPoint PPT presentation | free to download

A flowchart notation for state machines. Motivation. High-level description of clock-cycle ... ASM Diagram Pitfall. Conditional output boxes specify values ...

| PowerPoint PPT presentation | free to view

Increasing number of transistors, faster computers, and better design tools have ... Remember that there will be a quiz at the beginning of next class. ...

| PowerPoint PPT presentation | free to download

Suppose that we have a module foo ... parameter n = 8; output [n-1:0] out; input [n-1:0] a, b; foo foon[n-1:0](out,a,b); endmodule ...

| PowerPoint PPT presentation | free to download

Write result back to register. Store. Fetch operands from registers. Compute effective address ... Program Counter (PC) Adder. Operation. Fetch the instruction ...

| PowerPoint PPT presentation | free to view

Processor Design Datapath and Design All tables and diagrams in this presentation are from: D. Patterson and J. Hennessy, Computer Organization and Design: The ...

| PowerPoint PPT presentation | free to view

Ethan J Halpern, MD Director, Cardiac CT Thomas Jefferson University Patient Preparation Prior to CT Ask patient to refrain from stimulants (i.e. coffee) on the day ...

| PowerPoint PPT presentation | free to download

shorter clock cycle: cycle time constrained by longest step, not longest instruction ... controller must fire control lines in correct sequence and correct time ...

| PowerPoint PPT presentation | free to download