CISC - PowerPoint PPT Presentation

1 / 13

Title:

CISC

Description:

CISC & RISC. Computer Organization and Assembly Language #9. C. Vongchumyen 1 / 2004 ... After 1995 No more CISC CPU in market, Even Intel (IA64) CISC 's Problem ... – PowerPoint PPT presentation

Number of Views:28

Avg rating:3.0/5.0

Title: CISC

1

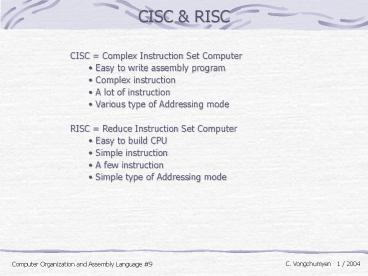

CISC RISC

- CISC Complex Instruction Set Computer

- Easy to write assembly program

- Complex instruction

- A lot of instruction

- Various type of Addressing mode

- RISC Reduce Instruction Set Computer

- Easy to build CPU

- Simple instruction

- A few instruction

- Simple type of Addressing mode

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9

2

RISC

- 1979 First RISC has been create by IBM

- Name IBM 801 by John Cocke

- Berkeley RISC by David A. Patterson

- Stanford MIPS by John L. Hennessy

- Supported by DARPA

- DARPA Defense Advanced Research Projects Agency

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9

3

RISC

- Hennesy MIPS

- IBM improve IBM 801 and use with IBM PC RT

- IBM PC RT is the first RISC computer

- But failed on market

- Next generation of RISC is PowerPC

- Sun Microsystems built Sparc base on Berkeley

RISC (1987) - PowerPC (1990)

- DEC Alpha (1993)

- After 1995 No more CISC CPU in market, Even

Intel (IA64)

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9

4

CISC s Problem

- A lot of instruction, Complex instruction

- Loop CX-1, CX 0 ?, Jump is yes

- Various type Addressing mode (8086 has 8 mode)

- Advancetage - Easy on programming

- - A few use of register

- Disadvancetage - Many from of Opcode

- - Cant fix instruction size

- - Complex decoder unit

- Must implement CU by Microcode or Microprogram

- (In early CPU use Hardwired)

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9

5

CISC Upgrade

- A lot of instruction, Various type of addressing

mode, - Many step in one instruction, Take more time.

- Use Pipeline to improve speed

- But Pipeline still have problem

Simple pipeline 2 stages Fetch and Execute

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9

6

RISC Design

- - A few instruction (lt 128), only necessary

instruction - - fix instruction length ( Data bus size)

- In fact not all instruction, but only 80 is OK

- - Simple addressing mode (not more than 4 type)

- 2. - 1 Clock operation (Most, except Div, Mul

etc) - - CU by Hardwired technique

- 3. - Only access memory with Load and Store

instruction - (Load/Store Architecture) to reduce addressing

mode - 4. - A lot of register (At least 32 registers)

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9

7

RISC s Compiler Design

- Old compiler try to use memory,

- Local variable keep in stack

- But for RISC use register,

- All local variable keep in register

- Call make a lot set of local variable, Use

register window - One window for one function one local variable

group - One window for global

- (all of register window are in CPU)

- And reduce register dependence

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9

8

PowerPC 7400 (G4)

- 32 bit CPU use in Macintosh

- 5 Execution units Floating Point Unit, Branch

Processing Unit, - Load/Store Unit and 2 unit of Integer Unit

- 1 Vector Unit use for SIMD instruction

- Maximum 3 instruction / clock

- 0.15 micron

- L1 cahce 32 32 KB

- 6.5 million transistor, 83 Square millimeter die

- Speed by SPECInt95 21.4, SPECfp95 20.4 at

450 MHz - by MIPs 825 MIPs (Pentium II 18.7 and 13.7

FPU) - BGA packaging (Ball Grid Array)

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9

9

PowerPC 7400 (G4)

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9

10

Sparc from Sun

- UltraSparc IIi 64 bit CPU

- 9 Execution unit, 4 Integer, 3 Floating Point

and 2 Graphics - L1 cache 16 16 KB

- Speed by SPECInt95 20.2, SPECfp95 22.5 at

480 MHz - 5.4 million transistors

- UltraSparc III (1999)

- Speed by SPECInt95 35, SPECfp95 60 at 600

MHz - L1 cache 16 16 KB

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9

11

UltraSparc IIi

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9

12

Alpha

- Alpha 21164 is a 64 bit CPU

- 4 Instruction / clock

- L1 cache 8 8 KB

- L2 cache 96 KB

- Fabrication on 0.35 micron

- Frequency 600 MHz

- Speed by SPECInt95 18, SPECfp95 27

- 2.4 Billion instruction per second

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9

13

Alpha 21164

C. Vongchumyen 1 / 2004

Computer Organization and Assembly Language 9