Architecture des Ordinateurs - PowerPoint PPT Presentation

1 / 63

Title:

Architecture des Ordinateurs

Description:

Communications entre processeur et l ments, mais aussi d' l ment ... un MAXimum est effectu entre tous les num ros de priorit d pos s par les arbitres un instant donn ... – PowerPoint PPT presentation

Number of Views:298

Avg rating:3.0/5.0

Title: Architecture des Ordinateurs

1

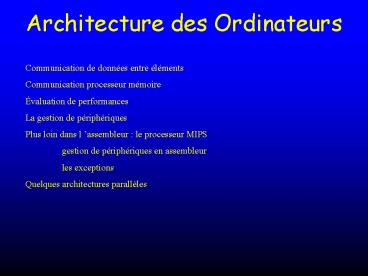

Architecture des Ordinateurs

Communication de données entre éléments Communicat

ion processeur mémoire Évaluation de

performances La gestion de périphériques Plus

loin dans l assembleur le processeur

MIPS gestion de périphériques en assembleur les

exceptions Quelques architectures parallèles

2

Échange de données

3

Rappel

Échange de données via bus d adresse

(unidirectionnel) bus de données (bidirectionnel)

Micro-processeur

Mémoire

4

Rappel

Terme générique de BUS englobe bus de donnés,

bus d adresse, signaux de commande

Micro-processeur

Mémoire

commandes

RAM

CPU

BUS

5

Autres dispositifs

- Communication avec dautres éléments

- clavier

- moniteur (carte vidéo)

- souris

- cartes contrôleur (USB, SCSI, Firewire)

- disques, lecteurs/graveurs

- imprimantes

- autres cartes (réseau, acquisition vidéo, etc)

6

Autres dispositifs

Communications entre processeur et éléments, mais

aussi délément à élément. Communication par

BUS BUS canal de communication plusieurs sortes

de BUS

imprimante

Écran

autres

CPU

RAM

Disque

BUS

7

Autres dispositifs

Éléments échangent des données via le bus. 1 seul

bus 1 seul dialogue à la fois 2 éléments

concernés le dialogue doit être organisé

stratégie de type Maître/Esclave Maître

donne des commandes via le bus Esclave

effectue laction demandée Exemples avec CPU

et Mémoire

8

Échanges CPU/Mémoire

Comment utiliser le (?) bus LE bus abus de

langage facilite la présentation en fait bus

d adresse, bus de données le plus souvent

pistes de cuivre contiguës apparence dun seul

bus. De plus signaux de commande pour piloter

lesclave En cas déchange CPU/mémoire Maître

CPU Esclave Mémoire

9

Échanges CPU/Mémoire

Établissement d un dialogue initié par le CPU

2 possibilités a) Lire une donnée à une

certaine adresse b) Écrire une donnée à une

certaine adresse quel élément fournit les

informations pour ces deux cas ? a) CPU

fournit adresse ou lire via le bus

d adresse commande READ via signaux de

commande RAM fournit valeur stockée via le bus

de données

10

Échanges CPU/Mémoire

b) CPU fournit adresse ou lire via le bus

d adresse commande WRITE via signaux de

commande valeur à écrire via le bus de

données la RAM est passive ? Les éléments du

dialogue sont ordonnés chronologiquement ! La RAM

ne peut pas traiter la requête instantanément

11

Échanges CPU/Mémoire

Cas a) CPU "voici ladresse, voici la commande

READ" quand la donnée sera-t-elle fournie par la

RAM ? La RAM fonctionne-t-elle bien ? RAM

fournit un premier accusé de réception de la

commande envoyée par le processeur "bien reçu

!" RAM temps dattente (délai de latence) pour

répondre une fois ce délai passé RAM "voici la

donnée, elle peut être lue" CPU "bien reçu !" RAM

"ok, je suis de nouveau disponible"

12

Échanges CPU/Mémoire

Cas b) CPU "voici ladresse, voici la commande

WRITE, voici la donnée" quand la donnée

sera-t-elle inscrite par la RAM ? La RAM

fonctionne-t-elle bien ? RAM fournit un premier

accusé de réception de la commande envoyée par le

processeur "bien reçu !" RAM temps dattente

(délai de latence) pour répondre une fois ce

délai passé RAM "j'ai écrit la donnée" CPU

"bien reçu !" RAM "ok, je suis de nouveau

disponible"

13

Types de BUS

Deux grandes familles de bus pour traiter ce type

d'échange BUS synchrone possède sa propre

fréquence, synchronisation des dispositifs par

rapport au BUS utilisation des fronts du signal

d'horloge du bus comme points de repère toute

transaction occupe un nombre entier de cycles de

bus

14

Types de BUS

Bus synchrone signal d'horloge ? représentation

?

Front descendant

t ns

Front montant

1 cycle de bus

Temps de montée non négligeable par rapport au

temps de cycle

15

Types de BUS

Toute information est prise en compte à

l'apparition d'un front (montant ou

descendant). Certains dispositifs utilisent les

deux fronts (ex RAM de type DDR) permet des

transferts par blocs (plusieurs données)

16

Types de BUS

BUS asynchrone pas d'horloge, les points de

repère sont fournis pas des signaux annexes de

synchronisation. Chaque élément pilote un tel

signal de synchronisation signal MSYN

synchronisation maître signal SSYN

synchronisation esclave

17

Chronogrammes de BUS

Reprise des exemples de dialogue Détail de la

transaction ,des signaux délivrés au fur et à

mesure du temps chronogramme de bus. Découpé ou

non en cycles ! Déroulement temporel ? Horloge

! Synchrone/asynchrone Même dialogue,

synchronisation différente.

18

Chronogrammes de BUS

Bus asynchrone Les signaux

ADRESSES

DONNEES

19

Chronogrammes de BUS

Relation de cause à effet entre signaux

20

Chronogrammes de BUS

Bus synchrone, fréquence F 40 MHz

C2

C1

C3

?

ADRESSES

MREQ

RD

WAIT

DONNEES

21

Chronogrammes de BUS

Contrainte de temps sur un bus synchrone

Adapter le temps de réponse de la mémoire à la

fréquence du bus. But minimiser les cycles en

wait-state car occupation du

bus monopolisation de l'UC (instruction en

cours) le bus peut être plus lent que

l'UC. L'UC s'organise en conséquence

(déséquencement)

22

Chronogrammes de BUS

Contrainte de temps sur un bus synchrone

Sur l'exemple précédent calcul du temps de

réponse de la mémoire en fonction des

caractéristiques du bus la mémoire commence à

réagir lorsque les signaux MREQ et RD sont

actifs. pourquoi pas de réaction avec le bus

d'adresse ?

23

Chronogrammes de BUS

Contrainte de temps sur un bus synchrone

Temps disponible dans chaque cycle cycle C1

reste (à peu près) 10 ns (après stabilisation

de MREQ et RD) cycle C2 on accepte un cycle en

wait-state 25 ns (la mémoire indique qu'elle

ne peut répondre) cycle C3 la donnée doit être

stable à la moitié du cycle 10 ns (car donnée

lue au front descendant d'horloge dans C3) total

45 ns limite supérieure du temps de réaction

avec 1 wait-state

24

Chronogrammes de BUS

Contrainte de temps sur un bus synchrone

Démarche inverse on connaît le temps de réponse

de la mémoire, combien y aura-t-il de cycles

d'attente ?

Nombre de cycles en wait-state

4

3

2

1

0

45 70 95 120

Temps de réponse (ns)

25

Mode bloc (bus synchrone)

Transfert de plusieurs données à la suite une

seule adresse fournie (sinon plusieurs

transactions) plusieurs valeurs concernées

(lecture ou écriture) donc valeurs localisées à

des adresses successives Utilité ? 1) taille de

donnée transmise taille D du bus de

données rappelez-vous le M68000 ! D ? taille M

d'une cellule mémoire ? taille R d'un registre

de données ! 2) Anticipation des accès futurs

26

Mode bloc (bus synchrone)

Ajout d'un signal supplémentaire BLOCK pour

demande de lectures successives. Principe le

CPU donne l'adresse, le nombre de données à

fournir (sur bus de données) et utilise un signal

BLOCK. La mémoire indique les cycles de

wait-state, puis transmet les données demandées à

raison d'une par cycle. Exemple d'un tel

chronogramme

27

Chronogramme de transfert de bloc

C2

C1

C3

C4

?

ADRESSES

BLOCK

MREQ

RD

WAIT

data

data

nombre

DONNEES

28

Comparaison de performance

Avec un bus synchrone transfert de N données

(lecture) mode 'simple' N transactions, chacune

consommant C cycles. décomposons C 1 cycle de

préparation W cycle(s) d'attente (wait

state) 1 cycle de lecture d'où C W2 d'où

temps total de transfert (on considère que les

transactions s'enchaînent sans temps mort) N.C

N.(W2)

29

Comparaison de performance

Avec un bus synchrone transfert de N données

(lecture) mode 'bloc' 1 transactions,

consommant C' cycles. décomposons C' 1 cycle

de préparation W cycle(s) d'attente (wait

state) N cycles de lecture (car mode

bloc) d'où temps total de transfert (on considère

que les transactions s'enchaînent sans temps

mort) 1.C' 1WN

30

Autres types de transactions

Communications avec autres dispositifs ? Avec le

même principe synchronisation d'un dialogue pré

établi entre maître et esclave, via le

bus. Maître "voici l'adresse, voici la

commande (et éventuellement la donnée)" Esclave

(au bout d'un certain temps) "Ok, bien reçu,

c'est fait" Maître "Bien reçu, j'ai terminé de

mon côté" Esclave "Je suis de nouveau

disponible"

31

Autres types de transactions

Tout dispositif ou périphérique est adressable

par le CPU où un autre dispositif (nous y

reviendrons plus tard)

32

Limites des familles de BUS

Bus synchrone présence de cycles transactions

en nombre entiers de cycles coût peu élevé

synchro faite par le bus. Efficace pour une

gamme de fréquence Bus asynchrone transactions

réglées au plus vite signaux supplémentaires coû

t élevé synchro faite par les périphériques

! Efficace quelle que soit le débit du

périphérique

33

Architecture des bus d'un PC

Basé sur des BUS synchrones. Quels types de bus

connus ? ISA / EISA ancien bus de PC PCI

(VLB) Bus générique à l'origine USB

Universal Serial Bus AGP Accelerated Graphic

Port cartes graphiques IDE/EIDE/(S)ATA

Integrated Drive Electronics / AT

Attachment Disques SCSI Disques

34

BUS Processeur

Carte Vidéo

Chipset 1 "NorthBridge"

RAM

BUS AGP

BUS MEM

Gfx RAM

BUS interne

USB FireWire

IDE ATA

Chipset 2 "SouthBridge"

Audio/Modem/Réseau

Clavier/souris/floppy/Midi

BUS PCI

35

Caractéristiques des bus PC

- Le FireWire (ou IEEE 1394-1995)

- partie intégrante de la norme SCSI-3, utilisation

d'un bus série. - Standard for a High Performance Serial Bus nom

de norme originale - FireWire nom déposé par Apple Computers Inc.

- Avantages prévus

- interface numérique (pas de CAN/CNA)

- taille réduite câble fin, peu coûteux

- Hot Plug and Play

- topologie flexible

- garantie de bande passante pour tous les

périphériques

36

Caractéristiques des bus PC

Le FireWire (ou IEEE 1394-1995) Destiné à relier

ordinateurs, produits manipulant de l'audio et

de la vidéo (caméscopes), imprimantes, scanners,

disques durs. Proche de l'USB, bande passante

bien supérieure, apparition de l'IEEE 1394b pour

concurrencer l'USB 2.0

37

Caractéristiques des bus PC

Le SCSI (Small Computer System Interface) créée

en 1986 à partir de l'interface SASI. Possibilité

de connecter des périphériques internes,

contrôleur évolué non prévu en série sur les

différents chipsets carte SCSI et matériels

onéreux en général. Gestion des accès et des

transferts réalisés par des puces spécialisées

décharge du processeur. Débit de 1,5 Mo/s

(SCSI-1) à 320 Mo/s (SPI-Ultra320)

38

Caractéristiques des bus PC

L'USB (Universal Serial Bus) Première version

commerciale de lUniversal Serial Bus,

linterface USB 1.1 permet de connecter à un

micro-ordinateur jusquà 127 périphériques pour

un débit maximal de 12 Mbits/s, soit 1.5 Mo/s, le

tout sur un bus série comme son nom lindique.

Principalement destiné aux périphériques lents,

linterface a été développée par Compaq,

Hewlett-Packard, Intel, Lucent, Microsoft, NEC et

Philips depuis 1994 pour aboutir sur le marché

grand public en 1998.

39

Caractéristiques des bus PC

- L'USB (Universal Serial Bus)

- Les principaux critères du développement de ce

bus ont été les suivants - Facilité dutilisation

- Solution bas-prix pour des périphériques pouvant

communiquer jusquà 12 Mbits/s - Transmission en temps réel de la voix, du son et

de vidéos compressées - Support de larchitecture CTI (Computer Telephony

Integration) - Facilité et ajout de possibilités dextensions

pour tout micro-ordinateur

40

Caractéristiques des bus PC

Le protocole LUSB prend en charge

principalement deux modes de transmission le

mode asynchrone, tout comme un port série

classique le mode isochrone, qui permet une

communication périodique et continue entre le

contrôleur maître et les périphériques. À chaque

milliseconde précisément, le contrôleur maître

transmet un paquet pour maintenir tous les

périphériques synchronisés. Il y a quatre sortes

de paquets les paquets de contrôle, les paquets

isochrones, les paquets en vrac et les paquets

dinterruption.

41

Caractéristiques des bus PC

Les paquets de contrôle servent à configurer des

périphériques, à leur donner des commandes et les

interroger sur leur statut. Les paquets

isochrones servent aux périphériques temps réel

comme les webcams et les téléphones, qui ont

besoin denvoyer ou de recevoir des données à des

intervalles de temps réguliers. Ils ont un délai

fixe, mais ne permettent pas de retransmission en

cas derreur. Les paquets en vrac servent pour

des transferts en direction ou en provenance dun

périphérique sans exigence de temps réel, comme

des imprimantes. Les paquets dinterruption sont

nécessaires parce que le USB ne support pas les

interruptions.

42

Caractéristiques des bus PC

Le bus AGP de la carte graphique en lui ouvrant

un canal direct d'accès à la mémoire, sans passer

par le contrôleur d'entrée-sorite. Ainsi le

contrôleur vidéo peut accéder directement à la

mémoire vive centrale Le port AGP 1X est cadencé

à 66 MHz, contre 33 MHz pour le bus PCI, ce qui

lui offre une bande passante de 264 Mo/s (pour le

bus PCI 132 Mo/s à partager entre les différentes

cartes), soit de bien meilleures performances,

notamment pour l'affichage de scènes 3D

complexes.

43

Caractéristiques des bus PC

- Le bus AGP

- Avec l'apparition du port AGP 4X, la bande

passante est passée à 1Go/s. - Maintenant la nouvelle norme est en AGP Pro 8x

avec une bande passante de 2Go/s. - Les débits des différentes normes AGP sont les

suivants - AGP 2X 66,66 MHz x 2(coef.) x 32 bits 533.67

Mo/s - AGP 4X 66,66 MHz x 4(coef.) x 32 bits 1,06

Go/s - AGP 8X 66,66 MHz x 8(coef.) x 32 bits 2,11

Go/s

44

Performances de bus

Dépend de la largeur de bus taille de la donnée

transmise Dépend du temps de transmission de la

donnée temps de présence sur le bus. Ce temps

dépend de la fréquence de bus. Soit un bus

synchrone de fréquence F (en MHz), et d'une

largeur de N bits (N fils de données). Fréquence

F nombre de changements d'état par seconde,

chaque ligne de bus est indépendante Débit

Dmax F. N (en bits/s-1).

45

Performances de bus

Applications numériques F 133 MHz, N64 bits

Dmax 64.133.106 bits.s-1, soit 1 064 000

000 octets/s, soit 0,99 Go/s, en divisant par

10243. Un constructeur fait ce calcul mais il

divise par 10003 1,064 Go/s. Sa mémoire est de

la DDR il double le débit 2,128 Go/s,

convertit et Mo et appelle sa mémoire PC2100

46

Performances de bus

Valable avec d'autres dispositifs ! Exemple avec

un dispositif vidéo Quelle doit être la bande

passante d'un bus vidéo pour réaliser un

affichage de 60 images/s avec une résolution de

1024 ? 768 en 32 bits ? combien d'octets occupe

une image 1024 ? 768 en 32 bits ? 1024 ? 768 ? 4

3 Mo ! (60 images de 3 Mo) /s 180 Mo/s

47

Performances de bus

Valable avec d'autres dispositifs ! Exemple avec

un dispositif vidéo Quelle doit être la bande

passante d'un bus vidéo pour réaliser un

affichage de 60 images/s avec une résolution de

1024 ? 768 en 32 bits ? combien d'octets occupe

une image 1024 ? 768 en 32 bits ? 1024 ? 768 ? 4

3 Mo ! (60 images de 3 Mo) /s 180 Mo/s

48

Gestion de bus, conflits

- Plusieurs éléments communicants

- un seul canal ? un seul dialogue à un instant

donné - arbitrage de l'accès au bus nécessaire !

(réseaux) - Arbitrage dynamique allouer le bus sur demande,

lorsqu'il est libre, à un maître potentiel qui le

demande via un signal Bus Request (BR) - il peut y avoir plusieurs demandes simultanées

choix d'une allocation/attribution

49

Gestion de bus, conflits

- suivant une priorité affectée de manière unique

à chaque maître potentiel - de manière "équitable" (pour éviter les pbs de

famine) - en combinant les deux politiques départager

équitablement deux demandes de même priorité - libération de bus peut intervenir de plusieurs

manières - fin de transaction

- sur demande le maître conserve le bus jusqu'à

une nouvelle demande - par préemption

50

Mécanisme matériels d'arbitres

- La réalisation du mécanisme d'arbitrage peut être

distribuée répartie entre les éléments

Arbitrage décentralisé - Cet arbitrage peut aussi être centralisé se

trouve sur un seul des modules connectés au bus,

ou sur un module dédié, nommé arbitre de bus - réalisation basée sur 3 signaux

- BR Bus Request demande de bus de la part des

maîtres potentiels - BA/BG Bus Acknowledge/Bus Grant attribution

de bus - BB Bus Busy bus occupé

51

Le Daisy Chaining

Structure en "guirlande" matérialisation de la

priorité des périphériques par leur position sur

le bus

Bus Grant

...

Périph 1

Périph 2

Périph n

Arbitre centralisé

Bus Request

Bus Busy

52

Le Daisy Chaining

Les éléments désirant prendre le contrôle du bus

émettent un signal BR la ligne "bus request"

arrivant à l'arbitre de bus réalise un OU

câblé. L'arbitre de bus ne voit donc qu'une

requête globale BR 2 options pour la suite du

traitement ligne BB gérée par l'arbitre ou

non a) BB gérée par l'arbitre si le bus est

libre arbitre émet BG à la guirlande, ce signal

est 'intercepté' par le dispositif le plus proche

de l'arbitre, le signal BB est activé et la

transaction de bus débute sinon pas d'émission

de BG

53

Le Daisy Chaining

b) BB non géré par l'arbitre l'arbitre émet BG

vers la guirlande lorsqu'un périphérique reçoit

ce signal, et s'il a émis une requête BR, il

regarde si le bus est libre (BB). Si oui, il

prend le contrôle du bus et signale que le bus

est occupé en activant le signal BB. Avantages

du daisy chaining simplicité de

réalisation inconvénients priorité statique,

lenteur de réponse, sensibilité aux pannes

54

Le Daisy Chaining exemple

Illustration du cas b) demandes BR simultanées de

2 et 4

Bus Grant

Périph 1

Périph 2

Périph 4

Périph 3

Arbitre centralisé

Bus Request

Bus Busy

55

Requête - Autorisation

Chaque module connecté au bus dispose de ses

propres lignes BG et BR reliées au contrôleur de

bus avantages absence de délai de réponse,

de sensibilité aux pannes d'un module, et le

caractère non statique de la priorité inconvénient

multiplication des lignes de contrôle

Périph 1

Périph 2

Périph 3

Arbitre centralisé

Bus Busy

56

Requête - Autorisation

Priorités gérées de manière dynamique

possibilité de définir une table des priorités,

associant à chaque signal BR issu d'un

périphérique une priorité indépendante de son

positionnement. Requête-autorisation permet de

faire des allocations équitables en gérant une

table des allocations accordées/refusées les

requêtes BR ne sont plus anonymes. Ex de contenu

de table de priorité dans un arbitre de bus n

de requête BR priorité courante de requêtes

BR satisfaites mise à jour des priorités selon

le nombre d'allocations allocation de ressource

dite à 'priorité tournante' (problème classique

rencontré dans d'autres domaines, notamment

ordonnancement de processus)

57

Arbitrage mixte

Combinaison des deux techniques précédentes

définition de 'groupes' de périphériques. Chaque

groupe dispose d'une ligne BR et d'une ligne BG

propre pour communiquer avec l'arbitre de bus (un

groupe est donc équivalent à un périphérique en

autorisation-requête) l'arbitre de bus délivre

donc un signal BG à ce groupe, ce signal est

ensuite traité par la technique de la guirlande

(daisy-chaining) au sein du groupe. (schéma)

58

Arbitrage décentralisé

Défaut de l'arbitrage centralisé si l'arbitre

tombe en panne ! Plus d'allocation de bus

possible, alors que les périphs fonctionnent

tous. On peut associer à chaque périphérique un

module d'arbitre décentralisé

périphérique

n de priorité

Bus Grant

Arbitre distribué

Bus busy

Bus numéro arbitrage

59

Arbitrage décentralisé

Chaque module possède un numéro de priorité

unique, et dialogue avec son propre

arbitre. L'arbitre place ce numéro sur le bus

numéro arbitrage (lignes de contrôle de bus) un

MAXimum est effectué entre tous les numéros de

priorité déposés par les arbitres à un instant

donné ce numéro est comparé, par chaque arbitre,

au numéro de périphérique dont dépend l'arbitre,

pour savoir s'il peut disposer du bus. Sinon

retrait du numéro Ne reste donc que le numéro du

périphérique pouvant prendre le bus, l'arbitre le

lui accorde.

60

Arbitrage décentralisé

Exemple N périphériques en arbitrage

décentralisé, les numéros 4,5 et 7 demandent

l'accès au bus sur la ligne MAX(4,5,7) 7

donc 4 et 5 retirent leur numéros !

61

Stratégies de priorités

Stratégie linéaire un numéro fixe est attribué à

chaque demandeur, les numéros sont rangés par

ordre de priorité décroissante. Exemple 4 L 3

L 1 L 2 signifie que le périphérique 4 est le

plus prioritaire, et que le 2 est le moins

prioritaire simple, mais risque de famine se

traduit facilement avec le daisy chaining

62

Stratégies de priorités

Stratégie Circulaire (Round Robin) la priorité

circule sur les demandeurs. Les numéros sont

placés dans une liste circulaire, et c'est le

demandeur dont le numéro est placé à droite du

dernier maître qui obtient la plus haute priorité

ex 4 R 3 R 1 R 2, signifie que le périphérique

le plus prioritaire est le 4 si le 2 était maître

du bus précédemment. Plus difficile que la

linéaire, mais évite les famines

63

Stratégies de priorités

Stratégie Cyclique pour chaque demandeur, on

garde l'antériorité des demandes précédentes

(c'est à dire le temps écoulé depuis la dernière

demande non satisfaite). Application d'une

stratégie linéaire sur les modules classés par

ordre d'antériorité décroissante. Ex 4 C 1 C 2 C

3. Possibilité de mixer ces différentes stratégies