Microoperations PowerPoint PPT Presentations

All Time

Recommended

Full Adders and Half Adders. Full Adder. Half Adder. ElE 385 - Fall 2001. Full Adders and Half Adders. Full Adder. Half Adder. FA. Ai Bi Ci-1. Ci Si. Ai Bi Ci-1 Si Ci ...

| PowerPoint PPT presentation | free to view

Register C. Register B. Register A. Used for highest bit from each register. Used for lowest bit ... Tri-State : 0, 1, High-impedance(Open circuit) Buffer ...

| PowerPoint PPT presentation | free to view

Micro Operation * MICROOPERATIONS Computer system microoperations are of four types: - Register transfer microoperations - Arithmetic microoperations - Logic ...

| PowerPoint PPT presentation | free to view

Computer Architecture I: Digital Design Dr. Robert D. Kent CPU Registers Register Transfer and Microoperations ...

| PowerPoint PPT presentation | free to download

... A set of registers Microoperations on these registers Control interface 9-2 Datapaths The arithmetic/logic unit ... One stage of logic ... shift, taking m clock ...

| PowerPoint PPT presentation | free to download

Title: REGISTER TRANSFER AND MICROOPERATIONS Author: Archilab Last modified by: sasikala Created Date: 3/2/1998 8:56:46 AM Document presentation format

| PowerPoint PPT presentation | free to download

Bus and Memory Transfers. Arithmetic Microoperations. Logic ... Parenthesis ( ) MAR, R2. Denotes a register. Letters & numerals. Examples. Description ...

| PowerPoint PPT presentation | free to download

Microprogrammed Control Unit Control Memory Sequencing Microinstructions Microprogram Example Design of Control Unit Microinstruction Format

| PowerPoint PPT presentation | free to download

... Control of Register Transfers Registers Register a collection of binary storage ... Large digital systems are hard to ... followed by numbers ...

| PowerPoint PPT presentation | free to view

Registers are constructed using flip-flops and combinational circuits that enable one to: ... OUTR :: Output buffer register. SCR :: Sequence counter register ...

| PowerPoint PPT presentation | free to download

... are bit-wise operations, i.e., they work on the individual bits of data ... useful for making logical decisions based on the bit value ...

| PowerPoint PPT presentation | free to download

Registers and Counters

| PowerPoint PPT presentation | free to download

7-7 Register-Cell Design A single-bit cell of an iterative combinational circuit connected to a flip-flop that provides the output forms a two-state sequential ...

| PowerPoint PPT presentation | free to view

Title: Diskreetne Matemaatika. S. Author: Alexander Sudnitson Last modified by: Aleksander Sudnitson Document presentation format: On-screen Show (4:3)

| PowerPoint PPT presentation | free to download

... end EUCLID; * architecture COMMON ... * Data path -2- Consider in our example the data path that is based upon some ALU which ... Input operands are 8-bit ...

| PowerPoint PPT presentation | free to download

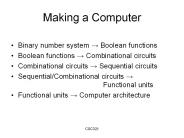

Computer Architecture Undergrad review

| PowerPoint PPT presentation | free to download

binary signals that activate the various data ... incrementing the contents of a register ... basic: add, subtract, increment, decrement, & complement ...

| PowerPoint PPT presentation | free to view

Making a Computer Binary number system Boolean functions Boolean functions Combinational circuits Combinational circuits Sequential circuits

| PowerPoint PPT presentation | free to download

MICROPROGRAMMED CONTROLLER Introduction Generalization of rom-based controller State-transition and output functions implemented using Table look-up Microinstruction ...

| PowerPoint PPT presentation | free to download

Info in status bits can be tested and actions initiated based on ... Incrementing CAR. Unconditional or conditional branch, depending on status bit conditions ...

| PowerPoint PPT presentation | free to download

A hard-wired control unit uses logic to generate the control signals needed to ... BUS MUX, memory, AR, PC, AC, DR, IR, TR, OUTR, R, IEN, AC, ALU, E, S, FGI, and FGO. ...

| PowerPoint PPT presentation | free to view

Title: Chapter 10 - Part 1 - PPT - Mano & Kime -3rd Ed Author: Kime & Kaminski Description: February 18, 2004 Version Last modified by: hexmoor Created Date

| PowerPoint PPT presentation | free to download

The fetch-decode-execute cycle is the series of steps that a computer carries ... Once in the IR, it is decoded to determine what needs to be done next. ...

| PowerPoint PPT presentation | free to view

The best way to define the operation of these modules is by specifying the ... are either represented using an alphabetically ordered list, or an enumerated list. ...

| PowerPoint PPT presentation | free to view

UNIT-II BASIC COMPUTER ORGANIZATION AND DESIGN REFERENCES Hayes P. John, Computer Architecture and Organisation, McGraw Hill Comp., 1988. Mano M., Computer System ...

| PowerPoint PPT presentation | free to view

a copy of the multiplicand is added to a partial product & the partial product ... multiplicand is loaded into register B from IN. multiplier is loaded into ...

| PowerPoint PPT presentation | free to view

http://panda.cs.ndsu.nodak.edu/~achapwes/PICmicro/keyboard/scancodes2.html ... Video (and movies) are a series of stills. If it goes fast enough ...

| PowerPoint PPT presentation | free to view

Design Reviews: Last Week of Classes ... Like production line book uses car wash example. Wash, rinse, dry. 36. Latency vs Throughput ...

| PowerPoint PPT presentation | free to download

Register Transfer and Micro operations Computer Organization TCS 303/TIT 304 Outline Register transfer Bus Transfer Memory Transfer Micro operations This Chapter ...

| PowerPoint PPT presentation | free to view

Chapter 4 MARIE: An Introduction to a Simple Computer

| PowerPoint PPT presentation | free to download

BASIC COMPUTER ORGANIZATION AND DESIGN Instruction Codes Computer Registers Computer Instructions Timing and Control Instruction Cycle

| PowerPoint PPT presentation | free to download

Strings and integers are stored in the same order. Doesn t allow values on non-word boundaries ... Adding use a stack CPU adds the top two elements of the stack, ...

| PowerPoint PPT presentation | free to download

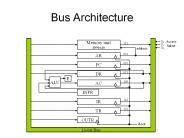

Bus Architecture S2 Access Select Memory unit 4096x16 111 S1 S0 address 001 AR 010 PC 011 DR E ALU 100 AC INPR 101 IR 110 TR OUTR clock 16-bit Bus

| PowerPoint PPT presentation | free to download

... Address = Rbase + 2scale Rindex + displacement x86 Instruction Encoding Variable length encoding Postfix bytes ... 4 under Linux Sorting in C ...

| PowerPoint PPT presentation | free to download

... than number of bits in either the Multiplicand or the Multiplier (up to 2n) ... Multiplicand 1000. Multiplier x 1001. 1000. 0000. 0000. 1000. Product ...

| PowerPoint PPT presentation | free to view

First models will use a 32-nm manufacturing process Ring architecture ... multicore and hyper-threading 4cores/8 multithread cache 8Mo (L3) 70 To, ...

| PowerPoint PPT presentation | free to download

trom : Control ROM delay. treg : Register delay. Chapter 5: Microprogrammed Control ... tstatus tsta_mux tseq trom treg} Total Time (T) = tclk nclk ...

| PowerPoint PPT presentation | free to view

UNIT-III CONTROL UNIT DESIGN INTRODUCTION CONTROL TRANSFER ... A micro-programmed control unit is flexible and allows designers to incorporate new and more powerful ...

| PowerPoint PPT presentation | free to view

T0: B = Binput; //Input multiplicand. T1: begin. A = 5'b00000; C = 1'b0; ... {C,A} = A B; //Add multiplicand. end. T3: begin. C = 1'b0; //Clear C ...

| PowerPoint PPT presentation | free to view

Chapter 2 Instructions: Language of the Computer Instruction Set The repertoire of instructions of a computer Different computers have different instruction sets But ...

| PowerPoint PPT presentation | free to view

Register Transfer Language (RTL) captures register transfers and it's components ... Must properly handle sign bit, overflow cond. ...

| PowerPoint PPT presentation | free to view

unit-iii control unit design introduction control transfer fetch cycle instruction interpretation and execution hardwired control microprogrammed control

| PowerPoint PPT presentation | free to download

Bus-Based Transfers. How about when there are lots of registers? ... Memory Transfers. Usually one or more buses associated with memory. Address. Data ...

| PowerPoint PPT presentation | free to download

Title: Author: Last modified by: Created Date: 2/28/2000 7:32:43 AM Document presentation format: ...

| PowerPoint PPT presentation | free to view

Input: architectural (behavioral) description in HDL (Verilog, ... 'E' existential path quantifier 'A' universal path quantifier 'X' next time 'F' eventually ' ...

| PowerPoint PPT presentation | free to download

Augend. Addend. Sum. Carry. Half-Adder. CSC321. Combinational ... Input 1 is call the 'Augend' Input 2 is called the 'Addend' Input 3 is call the 'Carry-in' ...

| PowerPoint PPT presentation | free to view

CENTRAL PROCESSING UNIT Introduction General Register Organization Stack Organization Instruction Formats Addressing Modes Data Transfer and Manipulation

| PowerPoint PPT presentation | free to download

4M 16 RAM chip gives us 4 megabytes of 16-bit memory locations. ... STORE Z,R1. Note: Two-address ISAs usually require one operand to be a register. 13 ...

| PowerPoint PPT presentation | free to view

Practical Applications; Conclusion. Outline. 8. Software ... Useful practical applications. of dynamically modifiable control. devices were discussed in ...

| PowerPoint PPT presentation | free to view

Computer Instructions Instructor : Oluwayomi Adamo The University of Adelaide, School of Computer Science * Chapter 2 Instructions: Language of the Computer * The ...

| PowerPoint PPT presentation | free to view

e.g Main frames (IBM 360) , mini computers (DEC PDP-8, PDP-11) ... Personal Computer (PCs), laptops, PDAs, servers, clusters ...

| PowerPoint PPT presentation | free to download

The Output Register (OUTR) holds an 8 bit character to be send to an output device ... When the 8-bit register OUTR is loaded from the bus, the data comes from the low ...

| PowerPoint PPT presentation | free to view

This is a bit pattern for a LOAD instruction as it would appear in the IR: ... have included two directives HEX and DEC that specify the radix of the constants. ...

| PowerPoint PPT presentation | free to view

The data AND the programs are coded in the same way, into binary, in ... Several formats, determined by the fields (codes can coexist in an instruction set) ...

| PowerPoint PPT presentation | free to download

... latches can be built from gates, and flip-flops can be built from latches. ... Many types of latches and Flip-Flops are available in SSI packages - DIP ...

| PowerPoint PPT presentation | free to view

Non-programmable (what you are implementing) Look ... Like a flowchart to express hardware algorithms. ASM describes sequence of events and timing relationships ...

| PowerPoint PPT presentation | free to download